# Department of Computer Science Faculty of Computing UNIVERSITI TEKNOLOGI MALAYSIA

SUBJECT : SCSR1013 DIGITAL LOGIC

SESSION/SEM : 2020/2021 SEMESTER 1

LAB 1 : COMBINATIONAL LOGIC

NAME 1 : QAISARA BINTI ROHZAN (A2OEC0133).

DATE : 17/11/2020

REMARKS :

MARKS:

#### **Lab** # 1

### **Introduction to Logic Circuits**

#### A. Objectives

The objectives of this laboratory are to introduce the student to:

- basic bread boarding and wiring techniques

- the use of input switches and output LEDs in generating truth tables for a combinational logic circuit

- to verify the characteristic of the basic gates

## B. Materials

- Breadboard

- 7408 Quad 2-input AND 1

- 7404 Hex Inverter 1

- 7400 Quad 2-input NAND 1

- 7432 Quad 2 input OR 1

- ETS-5000 Digital Training kit

### C. Introduction

This lab focuses on several practical issues related to bread boarding and testing combinational logic circuits. Several helpful points are made below.

<u>Wire gauge</u> - Use only 22 gauge wire. The breadboard may be damaged by forcing smaller gauge (larger diameter) wire into the holes.

<u>Wire color</u> - Use organized color schemes when wiring circuits. For example, use RED wire for all  $V_{cc}$  connections, BLACK wire for all ground connections, BLUE wire for all input switches, and YELLOW wire for all intermediate signal connections.

<u>Wire length and placement</u> - Use wires that are the appropriate length so that they can lie flat on the breadboard. Avoid running wires over IC's in case the IC's need to be removed.

<u>Testing IC's</u> - Chip tester is available in lab, always check your IC's before you begin wiring the circuit.

<u>Inserting IC's</u> - IC's are not difficult to insert in the socket strips once they have been properly adjusted. Brand new IC's are shipped with their pins bent apart from the vertical (typically 15° outward) in order to facilitate handling by automatic insertion equipment. Therefore, before an IC is used for the first time its pins must be bent back so that their spacing is vertical.

<u>IC Orientation</u> - Arrange all IC's in the same direction. This will facilitate connecting  $V_{cc}$  on each IC to a 5V strip on the breadboard and GND on each IC to a ground strip. If an IC is reversed (thus  $V_{cc}$  and ground are reversed), it may be destroyed. It is recommended that you begin wiring by making all  $V_{cc}$  and ground connections.

<u>IC Removal</u> - It is recommended that you use some sort of extraction tool for removing IC's. Attempts to remove IC's by hand may result in bent pins.

#### Monitoring the logic level of the circuit

Use the LED (at the top right of the digital kit) to monitor the logic level of the digital circuit. A GREEN indicates that the logic level is LOW (0) and a RED means the logic level is HIGH (1). If the LED does not lit, there is something wrong with the circuit. Switch off the power supply and recheck the circuit.

### Note: Please be certain that the MODE switch is flip to TTL not CMOS.

You can use a logic probe (at the bottom right of the digital circuit) to monitor the logic level of any node (point) of the circuit. **H** indicates logic HIGH (1), **L** means LOW (0) and **P** means pulse (the signal keeps on changing between HIGH and LOW).

### **Switches**

There are 8 toggle switches at the bottom row of the digital circuit. These switches will provide a logic input of HIGH (1) and LOW (0) to the circuit.

## D. Preiminary Work

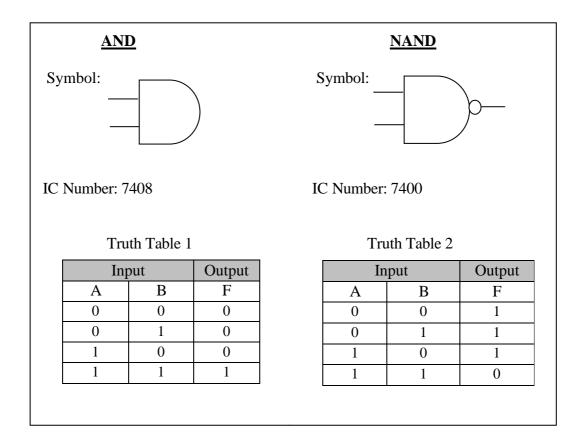

1. Draw a symbol, determine the IC number and produce a truth table for the following gate.

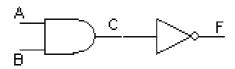

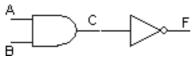

2. Complete the truth table for the following circuit.

Truth Table 3

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

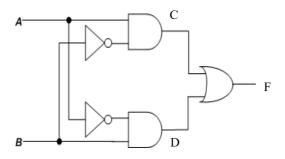

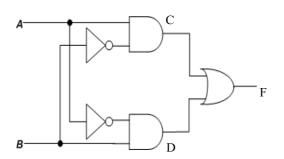

3. Write the Boolean expression for output C, D and F the following circuit.

$$C = A.\overline{B}$$

$$D = B.\bar{A}$$

$$F = C + D$$

4. Complete the truth table for the circuit in (3) based on the Boolean expression produced for C, D and F.

Truth Table 4

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

## E. Laboratory Work

#### Part 1

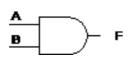

1. Construct Circuit 1 on the breadboard. Connect all inputs (A, B) to a switches and output F to LEDs.

Truth Table 5

| Input |   | Output |

|-------|---|--------|

| A     | В | F      |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

Circuit 1

2. Test Circuit 1 and fill in Truth Table 5 for the circuit response to all possible input combinations. The Truth Table 5 should match the Truth Table 1 prepared in the Preliminary Work.

| Fully     |  |

|-----------|--|

| Completed |  |

## Part 2

3. Construct Circuit 2 on the breadboard. Connect all inputs (A, B) to a switches and output C and F to LEDs.

Truth Table 6

| Circuit | 2 |

|---------|---|

|---------|---|

| A | В | C | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

- 4. Test Circuit 2; fill in Truth Table 6, for the circuit response to all possible input combinations.

- 5. Compare Truth Table 6 to Truth Table 2. What conclusion can you make?

Circuit 2 is a NAND Gate. It is combination of AND and NOT Gate

| Checked by: |

|-------------|

|             |

## Part 3

6. Construct circuit 3 on the breadboard. Connect all inputs (A, B) to a switches and output C, D and F to LEDs.

C D F A В 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1 0 0 0

Truth Table 7

Circuit 3

- 7. Test Circuit 3; fill in Truth Table 7 for the circuit outputs (C, D, and F) for all possible input combinations.

- 8. What single gate does Circuit 3 represent?

XOR Gate. Combination of AND, OR and NOT gates.

| Fully     |  |

|-----------|--|

| Completed |  |

| Partially |  |

|-----------|--|

| Partially |  |

|           |  |

| Completed |  |

| ا         |  |

| Checked by: |

|-------------|

|-------------|