**SEM 1 2020/2021: SECTION 01**

# Digital Logic

# LAB3

## **Students Information**

Name : 1. HANIS RAFIQAH BINTI HISHAM RAZULI (A20EC0041)

2. NIK SYAHDINA ZULAIKHA BINTI BADRUL HISHAM

(A20EC0108)

**Lecturer** : SIR FIROZ BIN YUSUF PATEL DAWOODI

### D. Preliminary Works

1) Determine the logic level for each input combinations in Table 1 so that the desired result can be realized.

Table 1

| Desired Result                                     | PRE | CLR | J | K | CLK      | Q |

|----------------------------------------------------|-----|-----|---|---|----------|---|

| Set initial value Q = 1                            | 0   | 0   | X | X | 1        | 1 |

| Output Q stays the same                            | 1   | 1   | 0 | 0 | #        | 1 |

| Output Q become 0, no change in asynchronous input | 1   | 1   | 0 | 1 | <b>#</b> | 0 |

| Output Q is not the previous Q                     | 1   | 1   | 1 | 1 | <b></b>  | 1 |

| RESET Q                                            | 1   | 1   | 0 | 1 | <b></b>  | 0 |

| SET Q                                              | 1   | 1   | 1 | 0 | <b>#</b> | 1 |

- 2) Answer all questions.

- a) Which state that JK flip-flop has, but not on SR flip-flop.

J=1, K=1

b) Identify whether the JK flip flop in 7476, is a positive-edge triggered or negative-edge triggered flip flop.

Positive edge.

#### E. Lab Activities

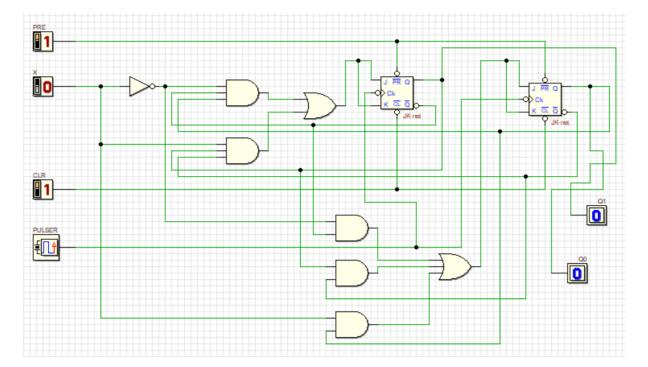

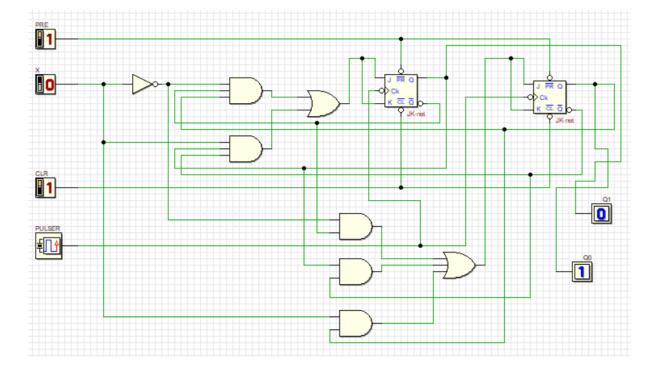

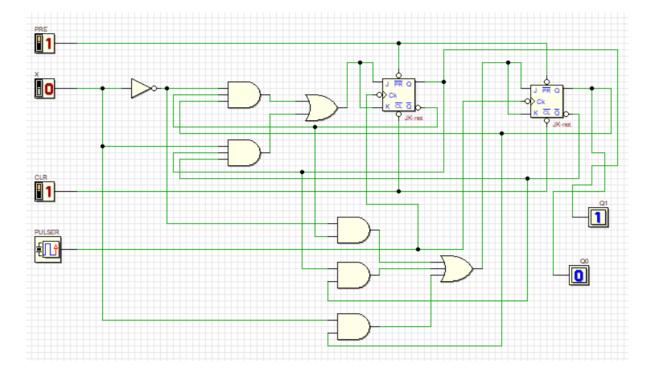

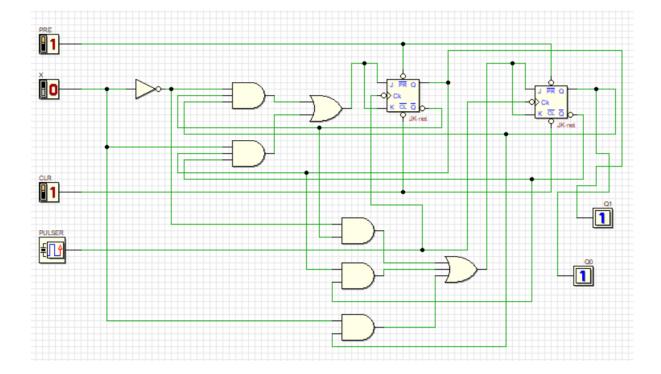

- 1) You are given a counter circuit as shown in Figure 4.

- 2) By using all materials and equipment's listed in section C, construct the physical circuit of Figure 4. (Make sure all ICs are connected to Vcc and GND).

3) Investigate the behavior of the counter by observing the next state of the counter for all combination of *Present State* and *X* values. Complete the Next State table of the counter in Table 2. Ensure the Switch 0 is in HIGH state. (0=LOW, 1=HIGH)

Table 2

| Switch 7 | Present State |            | Next State |            |  |

|----------|---------------|------------|------------|------------|--|

| X        | Q1<br>LED1    | Q0<br>LED0 | Q1<br>LED1 | Q0<br>LED0 |  |

| 0        | 0             | 0          | 0          | 1          |  |

| 0        | 0             | 1          | 1          | 0          |  |

| 0        | 1             | 0          | 1          | 1          |  |

| 0        | 1             | 1          | 1          | 1          |  |

| 1        | 0             | 0          | 0          | 0          |  |

| 1        | 0             | 1          | 0          | 0          |  |

| 1        | 1             | 0          | 0          | 1          |  |

| 1        | 1             | 1          | 1          | 0          |  |

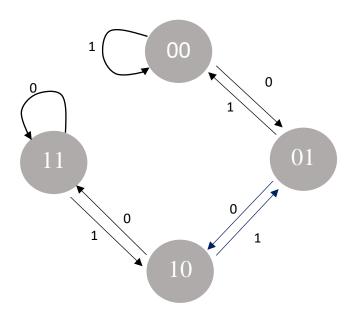

4) By referring to the Next-State in Table 2, sketch the state diagram of the counter.

- 5) By referring to the Next-State in Table 2 and the state diagram in (4), answer all questions.

- a) What is the main indicator to decide that the counter is a synchronous counter? The clock input of the flip-flop. The J-K flip-flops are connected together at the same time by the same clock signal.

- b) How many states are available for the counter and what are they? There are 4 states that are available. 00, 01,10 and 11.

- c) What is the function pf Switch 7 (X) in the circuit?It acts an an up-down counter. The counter will count up or down.

- d) What is the function of Switch 0 and Switch 1 in the circuit?

It acts as an asynchronous input. It has a control over the outputs. The inputs which are called preset (PRE) and clear (CLR) were put in a high state to allow a normal operation.

- e) Is the counter a saturated counter or recycle counter?

The counter is a saturated counter. It is fixed when it reaches the limit.

- 6) Referring to state diagram in 4, draw and built a synchronous counter using D flip-flop.

- a) Built the next state and transition table using the header in Table 3.

Table 3

| Input<br>X | Present State |    | Next State |     | D FF Transition |    |

|------------|---------------|----|------------|-----|-----------------|----|

|            | Q1            | Q0 | Q1+        | Q0+ | D1              | D0 |

| 0          | 0             | 0  | 0          | 1   | 0               | 1  |

| 0          | 0             | 1  | 1          | 0   | 1               | 0  |

| 0          | 1             | 0  | 1          | 1   | 1               | 1  |

| 0          | 1             | 1  | 1          | 1   | 1               | 1  |

| 1          | 0             | 0  | 0          | 0   | 0               | 0  |

| 1          | 0             | 1  | 0          | 0   | 0               | 0  |

| 1          | 1             | 0  | 0          | 1   | 0               | 1  |

| 1          | 1             | 1  | 1          | 0   | 1               | 0  |

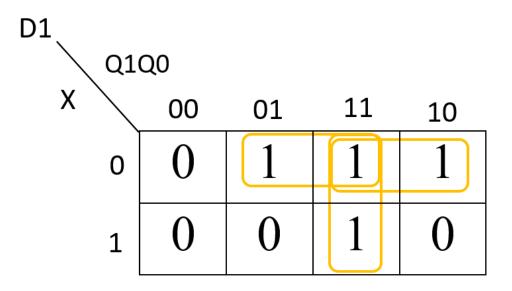

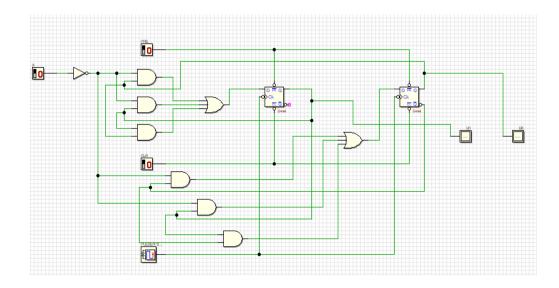

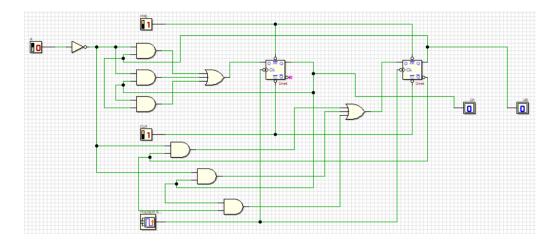

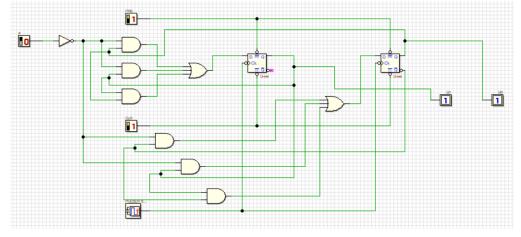

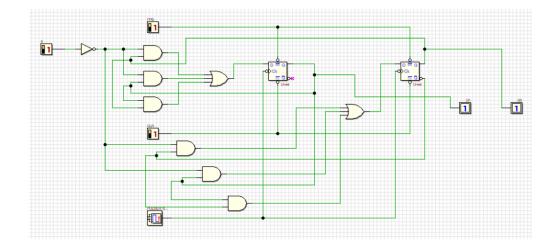

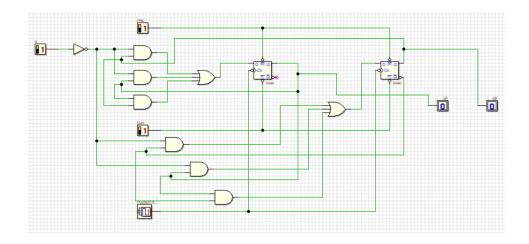

b) Get the optimized Boolean expression.

$$D1 = X'Q0 + X'Q1 + Q1Q0$$

$$D0 = X'Q0' + X'Q1 + Q1Q0'$$

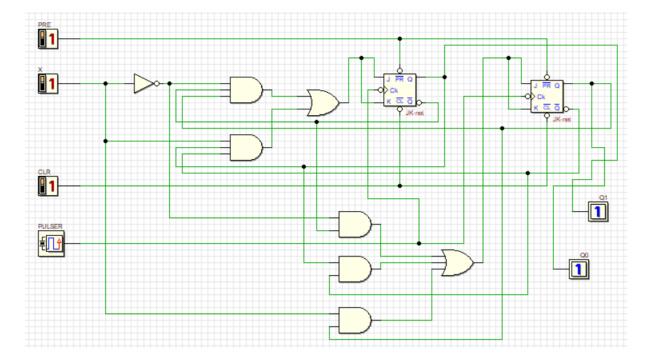

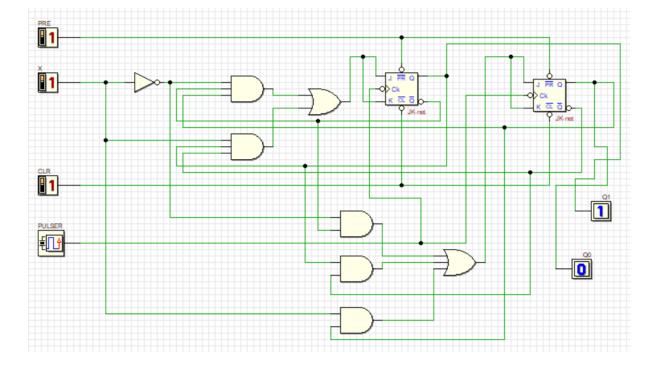

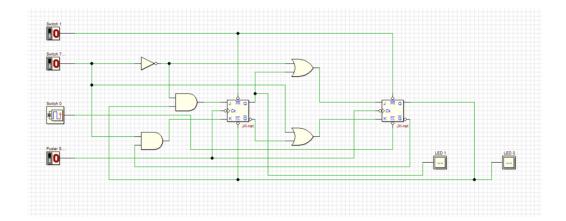

c) Draw the complete final circuit design in Deeds.

d) Simulate the circuit to prove your Table 3 is correct.

- 7) Repeat steps in Q(6) using T flip-flop.

- a) Built the next state and transition table using the header in Table 3.

Table 4

| Input<br>X | Presen | t State | Next State |     | T FF Transition |    |

|------------|--------|---------|------------|-----|-----------------|----|

|            | Q1     | Q0      | Q1+        | Q0+ | T1              | ТО |

| 0          | 0      | 0       | 0          | 1   | 0               | 1  |

| 0          | 0      | 1       | 1          | 0   | 1               | 1  |

| 0          | 1      | 0       | 1          | 1   | 0               | 1  |

| 0          | 1      | 1       | 1          | 1   | 0               | 0  |

| 1          | 0      | 0       | 0          | 0   | 0               | 0  |

| 1          | 0      | 1       | 0          | 0   | 0               | 1  |

| 1          | 1      | 0       | 0          | 1   | 1               | 1  |

| 1          | 1      | 1       | 1          | 0   | 0               | 1  |

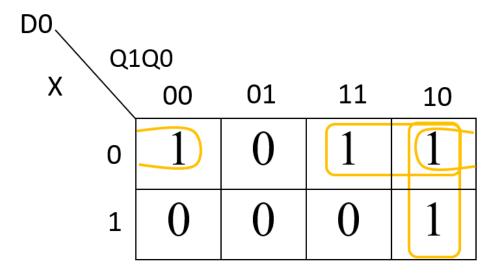

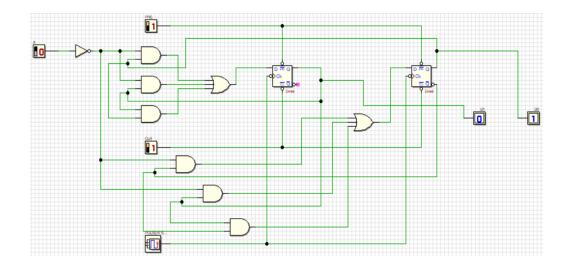

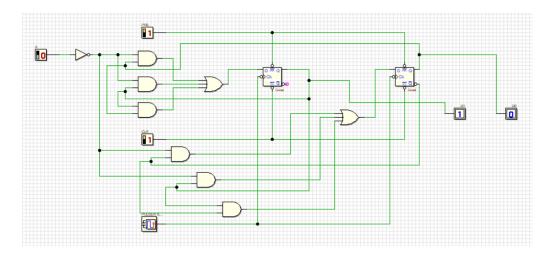

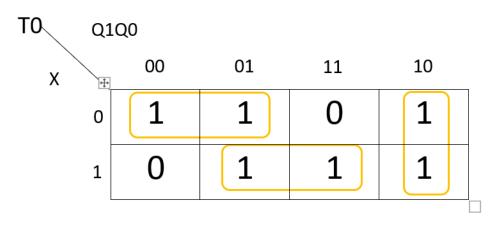

b) Get the optimized Boolean expression.

T1

| Q1Q0 |    |    |    |    |  |  |  |

|------|----|----|----|----|--|--|--|

| x \  | 00 | 01 | 11 | 10 |  |  |  |

| 0    | 0  | 1  | 0  | 0  |  |  |  |

| 1    | 0  | 0  | 0  | 1  |  |  |  |

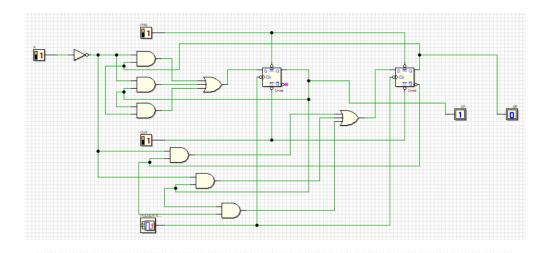

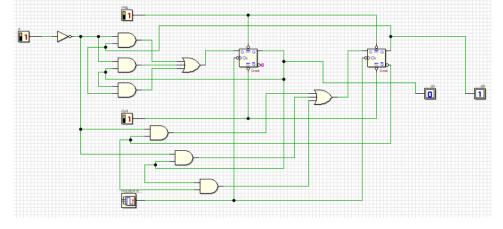

$$T1 = \overline{XQ1}Q0 + XQ1\overline{Q0}$$

$$T0 = \overline{X}\overline{Q1} + XQ0 + Q1\overline{Q0}$$

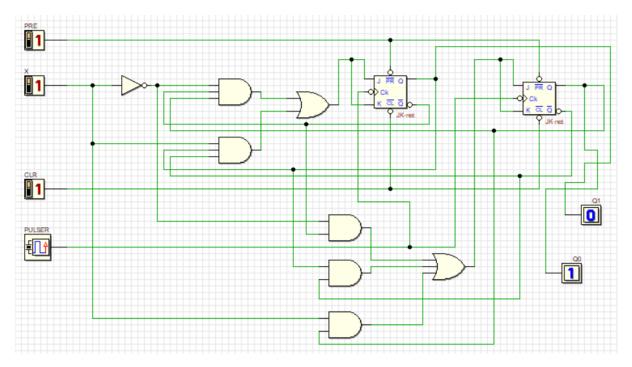

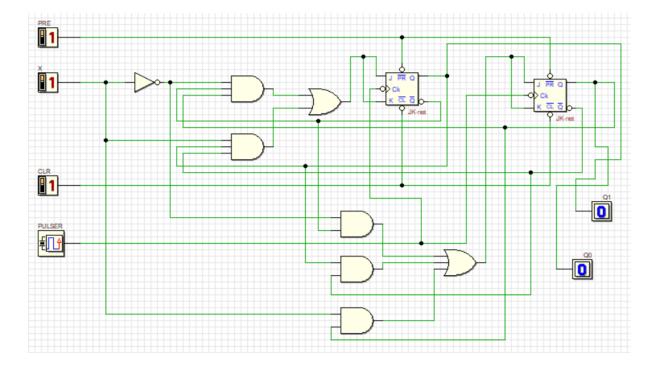

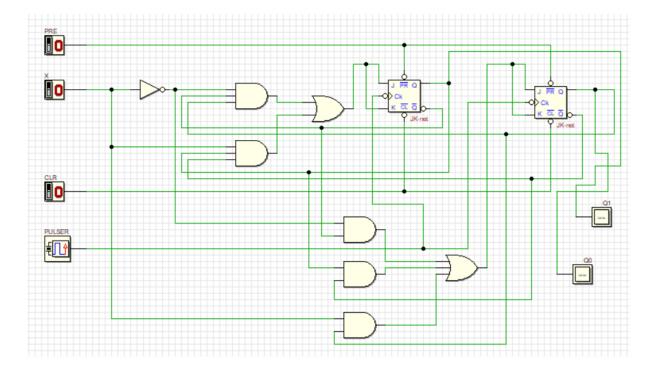

c) Draw the complete final circuit design in Deeds.

d) Simulate the circuit to prove your Table 3 is correct.