# Semester 2020/2021

Subject : Digital logic

Section : 06

Task : Lab 3

Submission: 28/01/2021

# **Group member**

Toya Lazmin Khan A20EC0284

G M SHAHEEN SHAH SHIMON A20EC0266

Lecturer: Dr. Yusuf Patel Dawoodi

## **D. Preliminary Works**

1.

Table 1

| Desired result            | PRE' | CLR' | J | К | CLK | Q |

|---------------------------|------|------|---|---|-----|---|

| Set initial value $Q = 1$ | 0    | 1    | Х | Х |     | 1 |

| Output Q stays the        | 1    | 1    | 0 | 0 | ₩   | 1 |

| same                      |      |      |   |   |     |   |

| Output Q become 0,        |      |      |   |   |     |   |

| no change in              | 1    | 1    | 1 | 1 | 1   | 0 |

| asynchronous input        |      |      |   |   |     |   |

| Output Q is not the       | 1    | 1    | 1 | 1 | ₩   | 1 |

| previous Q                |      |      |   |   |     |   |

| RESET Q                   | 1    | 1    | 0 | 1 | ₩   | 0 |

| SET Q                     | 1    | 1    | 1 | 0 | #   | 1 |

- 2. a) JK toggles when J is active (HIGH) and K is also active (HIGH)

- b) Negative edge triggered

## **E. Lab Activities**

1.

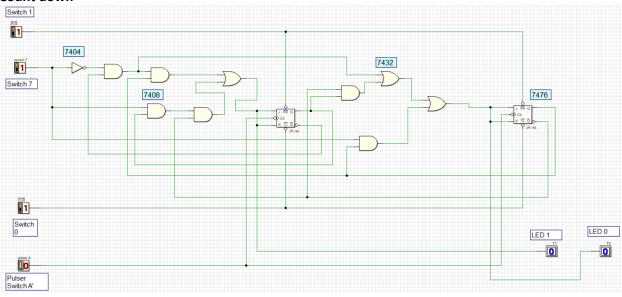

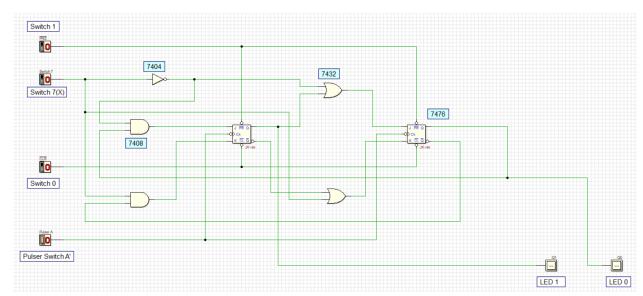

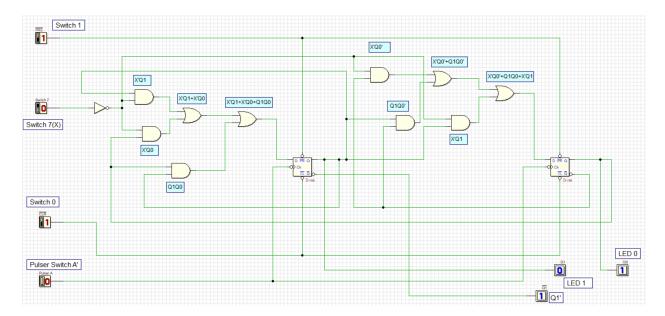

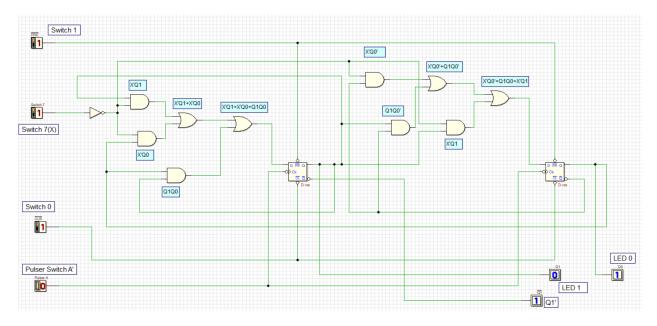

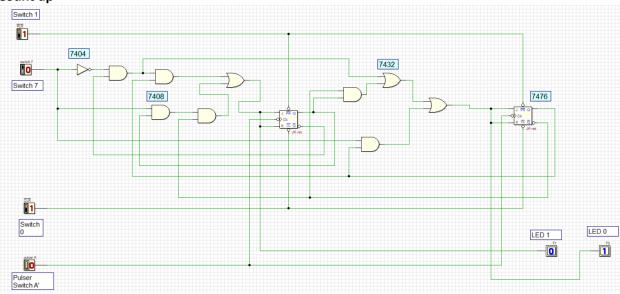

**Figure 4: A Synchronous Counter Circuit**

2.

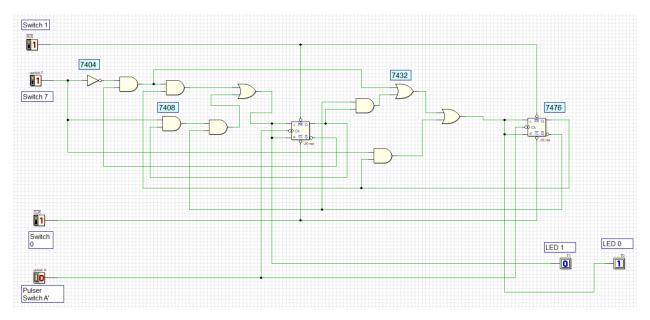

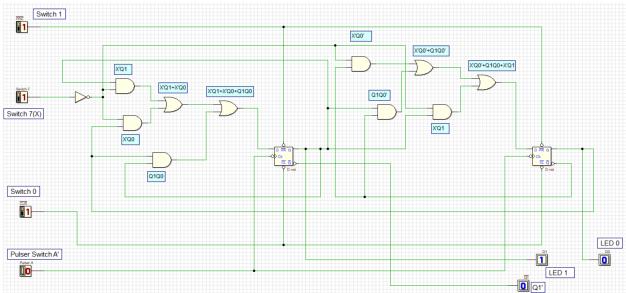

**Figure 5: A Synchronous Counter Circuit**

3.

Table 2

| Switch 7 | Prese | ent State | Next State |       |

|----------|-------|-----------|------------|-------|

| X        | Q1    | Q0        | Q1         | Q0    |

|          | LED 1 | LED 0     | LED 1      | LED 0 |

| 0        | 0     | 0         | 0          | 1     |

| 0        | 0     | 1         | 1          | 0     |

| 0        | 1     | 0         | 1          | 1     |

| 0        | 1     | 1         | 1          | 1     |

| 1        | 0     | 0         | 0          | 0     |

| 1        | 0     | 1         | 0          | 0     |

| 1        | 1     | 0         | 0          | 1     |

| 1        | 1     | 1         | 1          | 0     |

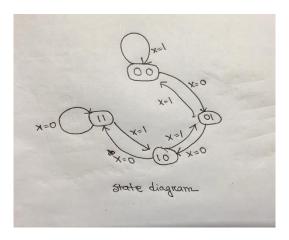

#### 4. State diagram

- **5. a)** Both flip-flop are triggered with same clock simultaneously

- **b)** There are 4 states: 00,01,10,11

- c) Switch 7 is count direction, it will determine if counter will go up or down. X=1(count down) and X=0 (count up)

**d)** There are asynchronous inputs, if both set to 1, JK can work synchronously. Switch 1 is active (HIGH), it presets output to 1 and when switch 0 is active, it clears the output to 0

**e)** Yes, it is saturated counter.

6. a) Table 3

| Switch 7 | Present State |       | Next State |       | D FF Transition |    |

|----------|---------------|-------|------------|-------|-----------------|----|

| X        | Q1            | Q0    | Q1         | Q0    | D1              | D0 |

|          | LED 1         | LED 0 | LED 1      | LED 0 |                 |    |

| 0        | 0             | 0     | 0          | 1     | 0               | 1  |

| 0        | 0             | 1     | 1          | 0     | 1               | 0  |

| 0        | 1             | 0     | 1          | 1     | 1               | 1  |

| 0        | 1             | 1     | 1          | 1     | 1               | 1  |

| 1        | 0             | 0     | 0          | 0     | 0               | 0  |

| 1        | 0             | 1     | 0          | 0     | 0               | 0  |

| 1        | 1             | 0     | 0          | 1     | 0               | 1  |

| 1        | 1             | 1     | 1          | 0     | 1               | 0  |

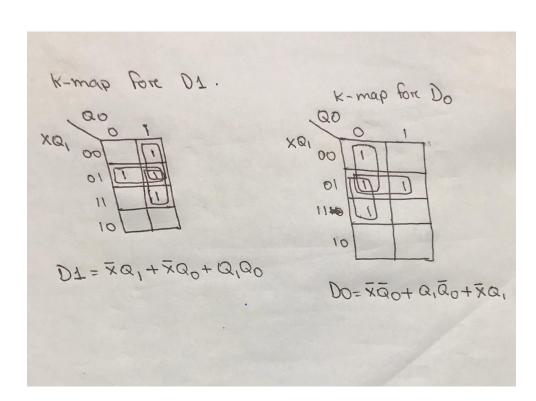

b)

Boolean expression:

D1 = X'Q1+ X'Q0+ Q1Q0

D0 = X'Q0' + Q1Q0' + X'Q1

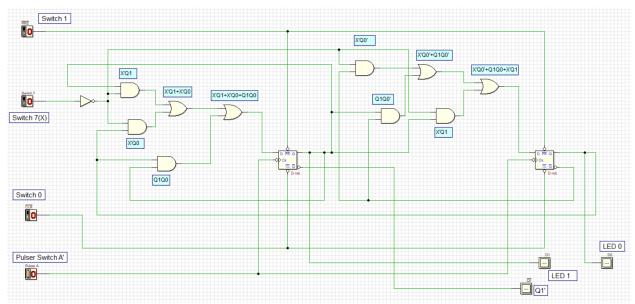

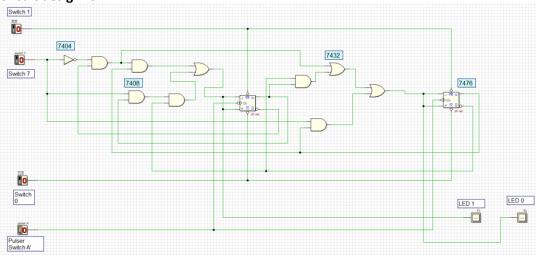

## Circuit design for D FF

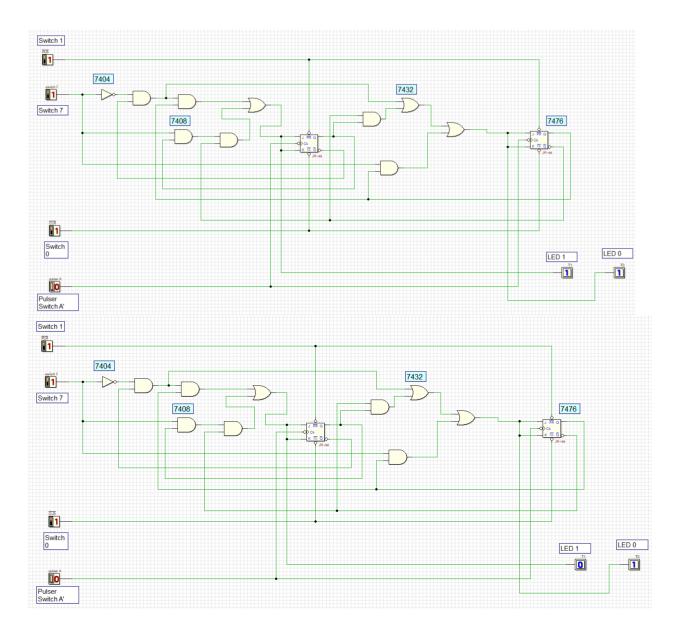

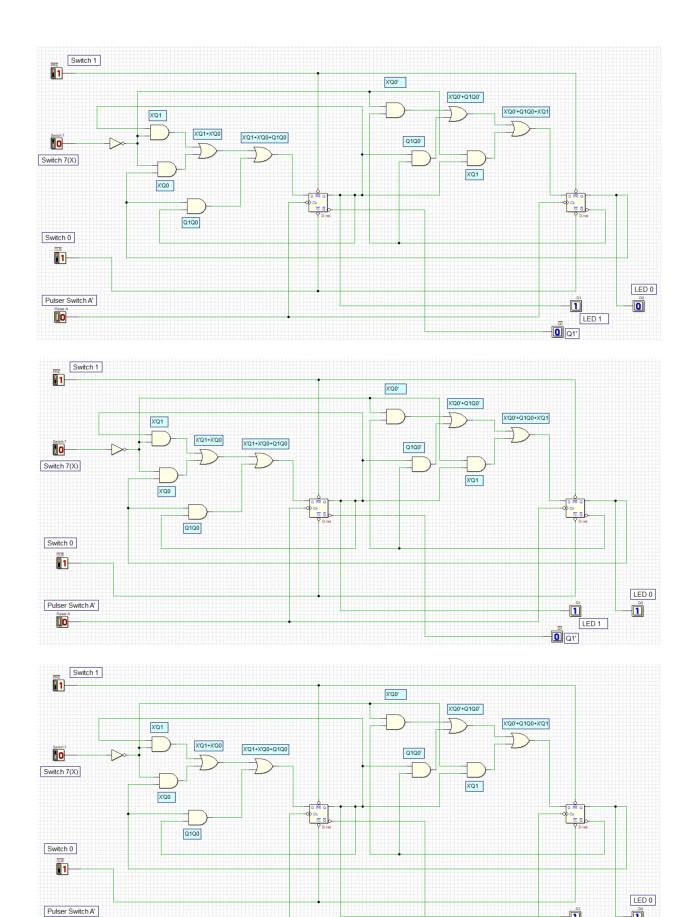

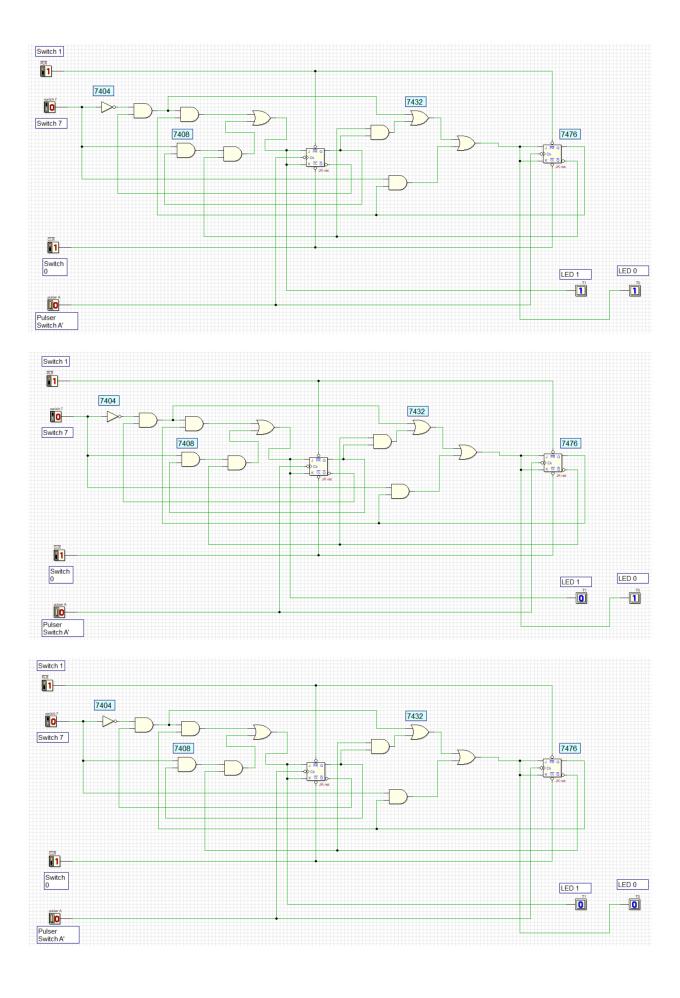

## c) Count up

LED 1

Q1'

Pulser A

#### **Count down**

7. a)

Table 4

| Switch 7 | Present State |       | Next State |       | D FF Transition |    |

|----------|---------------|-------|------------|-------|-----------------|----|

| X        | Q1            | Q0    | Q1         | Q0    | T1              | T0 |

|          | LED 1         | LED 0 | LED 1      | LED 0 |                 |    |

| 0        | 0             | 0     | 0          | 1     | 0               | 1  |

| 0        | 0             | 1     | 1          | 0     | 1               | 1  |

| 0        | 1             | 0     | 1          | 1     | 0               | 1  |

| 0        | 1             | 1     | 1          | 1     | 0               | 0  |

| 1        | 0             | 0     | 0          | 0     | 0               | 0  |

| 1        | 0             | 1     | 0          | 0     | 0               | 1  |

| 1        | 1             | 0     | 0          | 1     | 1               | 1  |

| 1        | 1             | 1     | 1          | 0     | 0               | 1  |

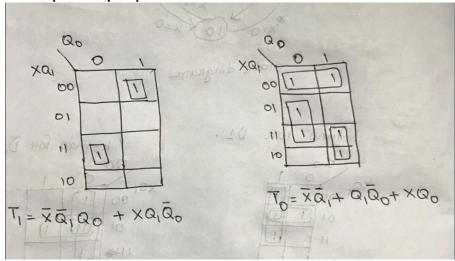

k-map for T flip-flop

Boolean expression: T1=X'Q1'Q0 + XQ1Q0' T0=X'Q1' + Q1Q0' + XQ0

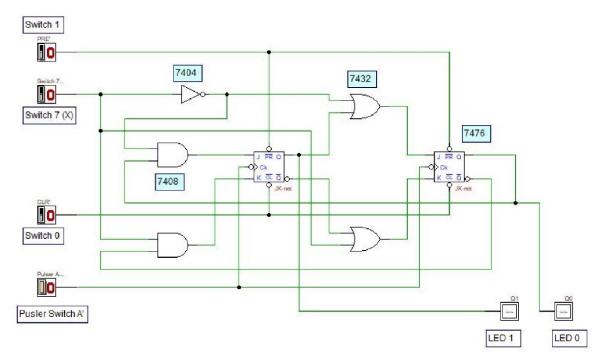

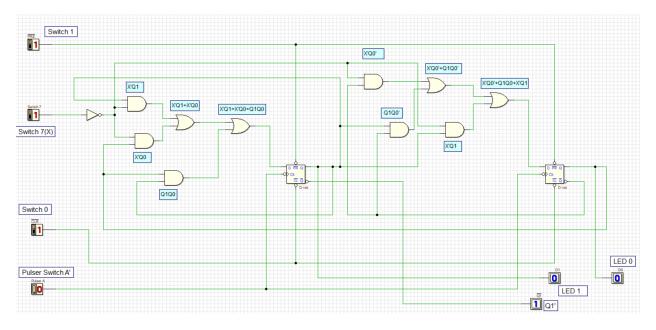

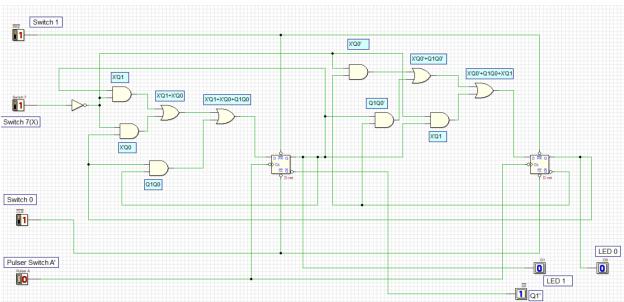

Circuit design for T FF

# **Simulation**

#### Count up

## **Count down**