# **SECR1013 DIGITAL LOGIC**

# **Lab 1 Combinational Logic**

Lecturer Name: Mr Firoz bin Yusuf Patel Dawoodi Section 08

Prepared by: Group 5

| NAME          | MATRIC NO |

|---------------|-----------|

| WONG HUI SHI  | A20EC0169 |

| TEOH WEI JIAN | A20EC0229 |

Submission Date: 21 DEC 2020

### **Lab 1 Combination Logic**

#### **D**. Preiminary Work

#### **Question 1**

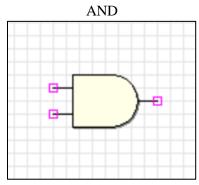

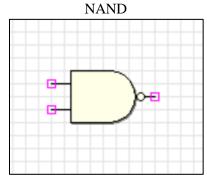

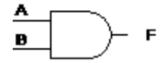

Draw a symbol, determine the IC number and produce a truth table for the following gate.

IC Number: 7408

Truth Table 1

| Input |   | Output |

|-------|---|--------|

| A     | В | F      |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

IC Number: 7400

Truth Table 2

| Input |   | Output |

|-------|---|--------|

| A     | В | F      |

| 0     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 0      |

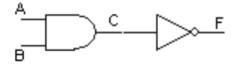

### **Question 2**

Complete the truth table for the following circuit.

Truth Table 3

| A | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

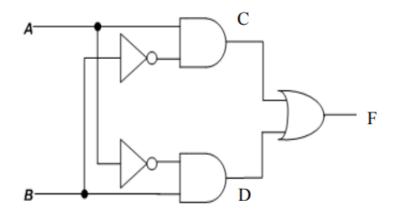

### **Question 3**

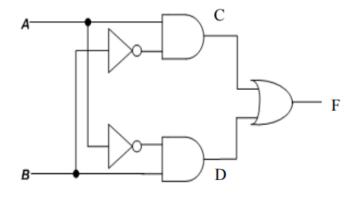

Write the Boolean expression for output C, D and F for the following circuit.

$$C = A\overline{B}$$

$$D = \overline{A}B$$

$$F = A\overline{B} + \overline{A}B$$

### **Question 4**

Complete the truth table for the circuit in (3) based on the Boolean expression produced for C, D and F.

Truth Table 4

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

## E. Laboratory work

### <u>Part 1</u>

1. Construct Circuit 1 on the breadboard. Connect all inputs (A, B) to a switches and output F to LEDs.

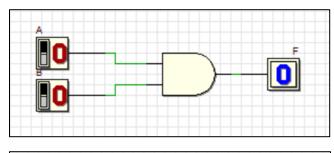

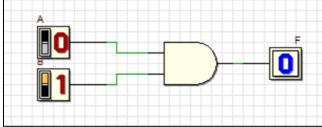

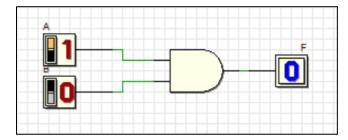

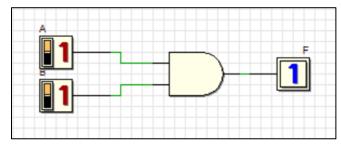

Circuit 1

Screenshots for result Circuit 1 by using Deeds-DcS:

2. Test Circuit 1 and fill in Truth Table 5 for the circuit response to all possible input combinations. The Truth Table 5 should match the Truth Table 1 prepared in the Preliminary Work.

Truth Table 5

| Input |   | Output |

|-------|---|--------|

| A     | В | F      |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

#### Part 2

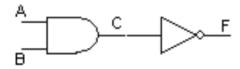

3. Construct Circuit 2 on the breadboard. Connect all inputs  $(A,\,B)$  to a switches and output C and F to LEDs

Circuit 2

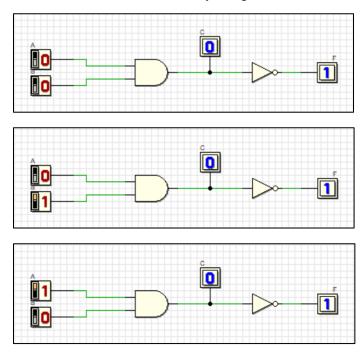

Screenshots for result Circuit 2 by using Deeds-DcS:

4. Test Circuit 2, fill in Truth Table 6, for the circuit response to all possible input combinations.

Truth Table 6

| A | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

5. Compare Truth Table 6 to Truth Table 2. What is the conclusion can you make?

The result of the truth table for both Truth Table 2 and Truth Table 6 are the same, the conclusion is circuit 2 represents NAND gate.

#### Part 3

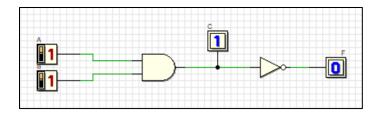

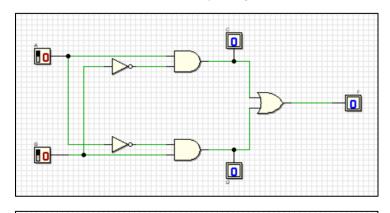

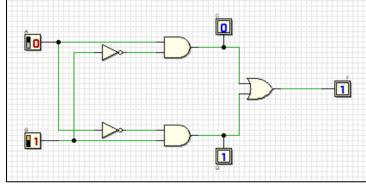

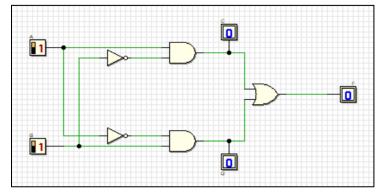

6. Construct circuit 3 on the breadboard. Connect all inputs (A, B) to a switches and output C, D and F to LEDs.

Circuit 3

# Screenshots for result Circuit 3 by using Deeds-DcS:

7. Test Circuit 3; fill in Truth Table 7 for the circuit outputs (C, D, and F) for all possible input combinations.

Truth Table 7

| A | В | С | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

8. What single gate does Circuit 3 represent?

Circuit 3 represent XOR gate.