## Department of Computer Science Faculty of Computing UNIVERSITI TEKNOLOGI MALAYSIA

SUBJECT : SCSR1013 DIGITAL LOGIC

SESSION/SEM : 1/2020/2021

LAB 2 : COMBINATIONAL LOGIC CIRCUIT DESIGN

SIMULATION

NAME 1 Woon Zi Jian A20EC0171

NAME 2 Gui Yu Xuan A20EC0039

DATE : 14/1/2021

REMARKS :

MARKS:

### D. Lab Activities

### Part 1

Simulating logic circuit, construct truth table and timing diagram with Deeds.

Given Boolean expression as follow:

$$Y = AB + BC + AC$$

Convert the non-standard Boolean expression into standard form.

$$Y = AB\bar{C} + ABC + \bar{A}BC + A\bar{B}C$$

2. Based on standard form expression, complete the following truth table.

|   | INPUT |   |   |  |  |

|---|-------|---|---|--|--|

| A | В     | C | Y |  |  |

| 0 | 0     | 0 | 0 |  |  |

| 0 | 0     | 1 | 0 |  |  |

| 0 | 1     | 0 | 0 |  |  |

| 0 | 1     | 1 | 1 |  |  |

| 1 | 0     | 0 | 0 |  |  |

| 1 | 0     | 1 | 1 |  |  |

| 1 | 1     | 0 | 1 |  |  |

| 1 | 1     | 1 | 1 |  |  |

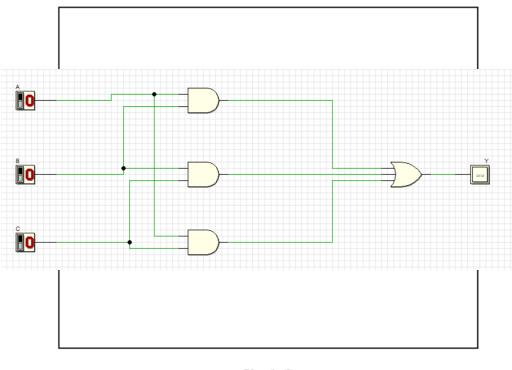

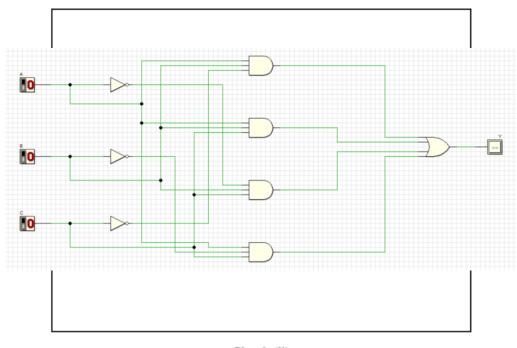

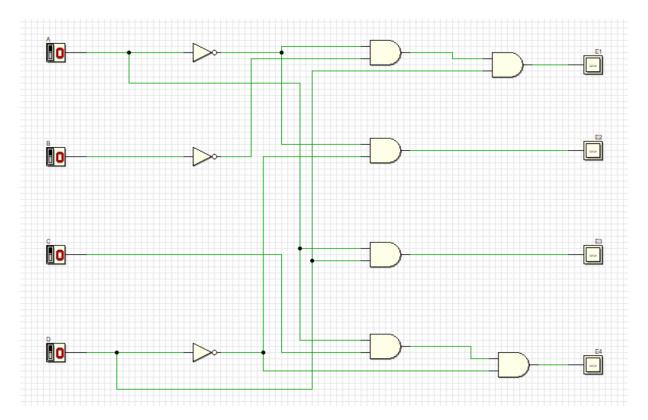

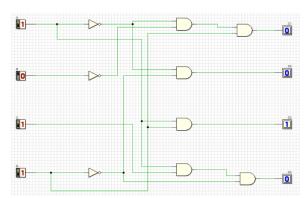

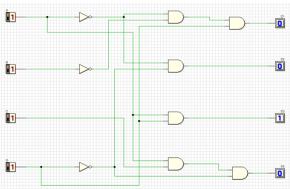

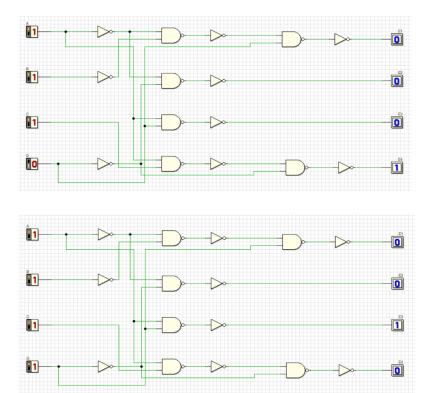

- 3. Using Deeds Simulator, draw the following circuits:

- a) Circuit (i) for non-standard form (based on the given expression).

Circuit (i)

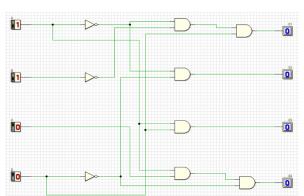

b) Circuit (ii) for standard form (from your answer in question (1)).

Circuit (ii)

## **Non-standard SOP circuit**

# **Standard SOP circuit**

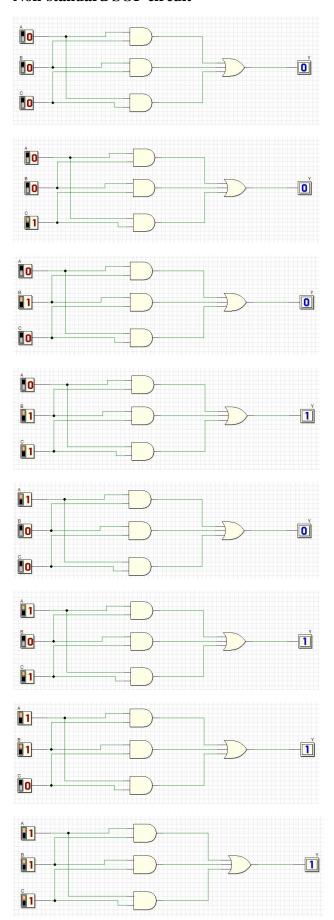

4. Simulate these two circuits in step (3) and complete their truth table.

Compare the simulation result for these two truth tables. What is your conclusion?

Circuit (i)

|   |       |   | OUTPUT |  |  |  |

|---|-------|---|--------|--|--|--|

|   | INPUT |   |        |  |  |  |

| Α | В     | С | Y      |  |  |  |

| 0 | 0     | 0 | 0      |  |  |  |

| 0 | 0     | 1 | 0      |  |  |  |

| 0 | 1     | 0 | 0      |  |  |  |

| 0 | 1     | 1 | 1      |  |  |  |

| 1 | 0     | 0 | 0      |  |  |  |

| 1 | 0     | 1 | 1      |  |  |  |

| 1 | 1     | 0 | 1      |  |  |  |

| 1 | 1     | 1 | 1      |  |  |  |

Circuit (ii)

|   | INPUT |   |   |  |  |  |

|---|-------|---|---|--|--|--|

| Α | ВС    |   | Y |  |  |  |

| 0 | 0     | 0 | 0 |  |  |  |

| 0 | 0     | 1 | 0 |  |  |  |

| 0 | 1     | 0 | 0 |  |  |  |

| 0 | 1     | 1 | 1 |  |  |  |

| 1 | 0     | 0 | 0 |  |  |  |

| 1 | 0     | 1 | 1 |  |  |  |

| 1 | 1     | 0 | 1 |  |  |  |

| 1 | 1     | 1 | 1 |  |  |  |

### Conclusion:

Standard SOP form is all variables appear in each product term of expression.

It will produce the same output as nonstandard form of SOP. This is because nonstandard form of SOP is the simplification of standard SOP form.

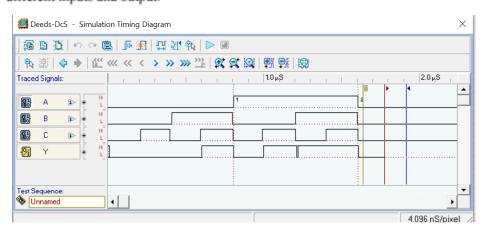

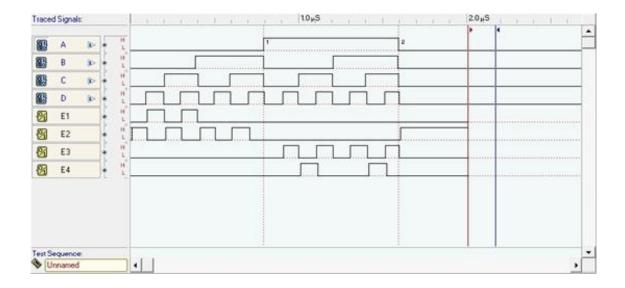

Simulate output of circuit (ii) with Timing Diagram. Illustrate some examples of different inputs and output.

Output Y is high when one of the inputs is low or all the input is high. Output Y is low when all the input is low or one of the inputs is high.

## **Experimental Steps**

Complete Truth Table 1 for Digital Fault Diagnose Circuit. Use variables A, B, C and D as inputs; E1, E2, E3 and E4 as outputs.

Truth Table 1

|    | 0 15 | even  | A = | positive | - Waa | the, w  | here o | = positi | rue, 1 = regative |

|----|------|-------|-----|----------|-------|---------|--------|----------|-------------------|

| )  |      | Input |     |          |       | Outputs |        |          |                   |

|    | A    | В     | C   | D        | EI    | EZ      | E3     | Eq       |                   |

| 0  | 0    | 0     | U   | 0        | 0     | 1       | 0      | 0        |                   |

| 1  | 0    | 0     | 0   | 1        | 1     | 0       | 0      | 0        |                   |

| 2  | 0    | D     | 1   | 0        | 0     | 1       | 0      | 0        |                   |

| 3  | 0    | 0     | 1   | 1        | ×     | ×       | X      | ×        |                   |

| U  | 0    | 1     | 0   | 0        | 0     | 1       | 0      | 0        |                   |

| 2  | 0    | 1     | 0   | 1        | ×     | ×       | X      | X        |                   |

| 6  | 0    | 1     | 1   | 0        | X     | *       | X      | ×        |                   |

| 7  | 0    | 1     | 1   | 1        | 0     | 0       | 0      | 0        |                   |

| -8 | 1    | 0     | 0   | 0        | 0     | 0       | 0      | 0        |                   |

| -7 | 1    | 0     | 0   | 1        | ×     | ×       | X      | ×        |                   |

| -6 | 1    | 0     | 1   | 0        | ×     | ×       | X      | *        |                   |

| -5 | 1    | 0     | 1   | 1        | 0     | 0       | 1      | 0        |                   |

| 4  | 1    | 1     | 0   | 0        | ×     | ×       | X      | X        |                   |

| -3 | 1    | 1     | 0   | 1        | 0     | 0       | 1      | 0        |                   |

| -2 | 1    | 1     | 1   | 0        | 0     | 0       | 0      | 1        |                   |

| -1 | 1    | .1    | 1   | 1        | 0     | 0       | 1      | 0        |                   |

2. Using K-MAP, get minimized SOP Boolean expressions for E1, E2, E3 and E4 circuits.

| AB 60 00 01 11 10 | ABCO 60 01 11 10  |

|-------------------|-------------------|

| 00 0 0 5 0        | 06 0 0 × 0        |

| 01 0 × 0 ×        | 01 0 × 0 ×        |

| 11 × 0 0 0        | 11 × 11 0         |

| 10 0 × 0 ×        | 10 0 × 1) ×       |

| EI = ĀBD          | E3 = A0           |

|                   |                   |

| AS CD 00 01 11 10 | AS CO 00 01 11 10 |

| 00 1 0 × 1        | 00 0 0 0 0        |

| 01 1 × 0 ×        | 01 0 × 0 ×        |

| 11 × 0 0 0        | 11 × 0 0          |

| 10040×            | 100 × 0 ×         |

| E2 = ÃŌ           | E4 = ACD          |

|                   |                   |

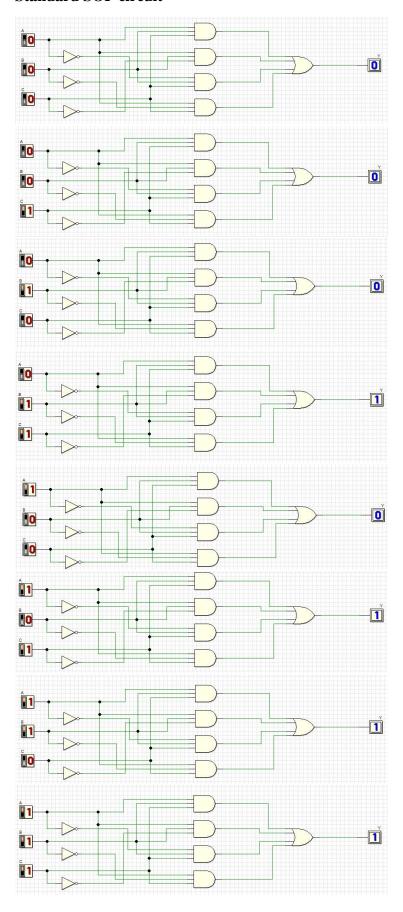

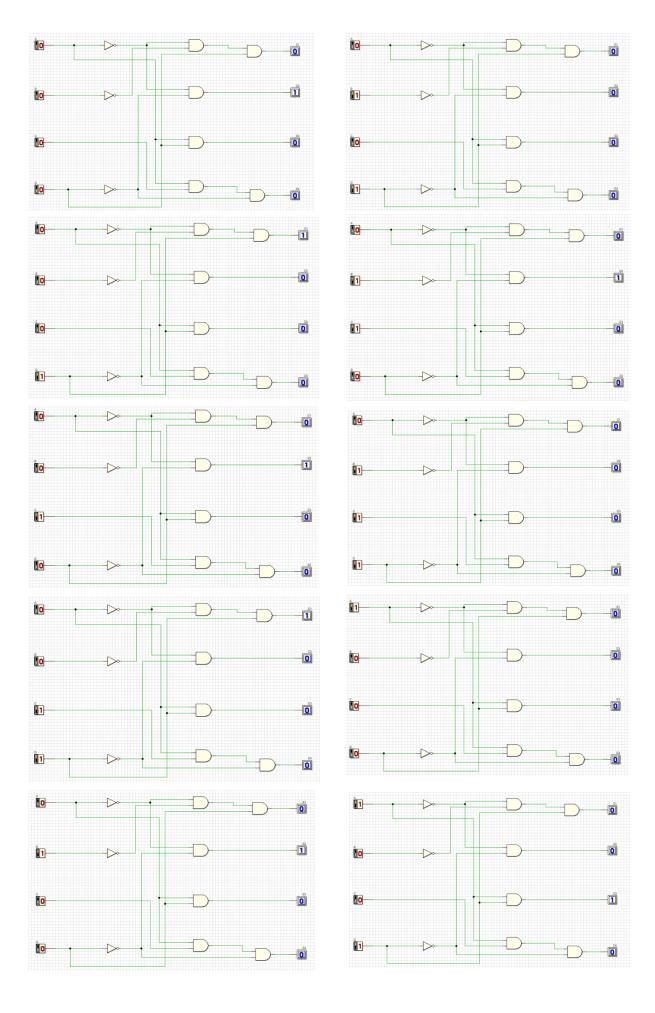

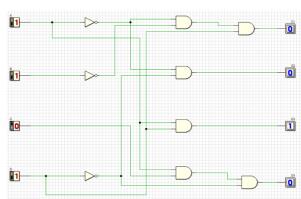

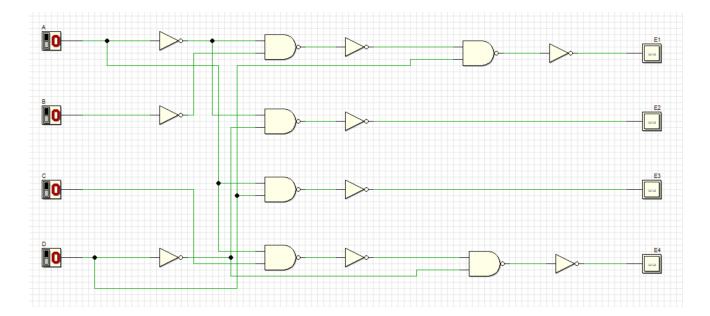

From the Boolean expression in the step (2), draw your final E1, E2, E3 and E4 circuits using 2 input basic gates (AND, OR, NOT). Use Deeds Simulator.

- 4. Simulate the Deeds circuit in step (3):

- a) Update Truth Table 2 based on the simulation result.

Truth Table 2

|   | INPU' | ΓS |   | OUTPUTS |    |    |    |

|---|-------|----|---|---------|----|----|----|

| A | В     | C  | D | E1      | E2 | E3 | E4 |

| 0 | 0     | 0  | 0 | 0       | 1  | 0  | 0  |

| 0 | 0     | 0  | 1 | 1       | 0  | 0  | 0  |

| 0 | 0     | 1  | 0 | 0       | 1  | 0  | 0  |

| 0 | 0     | 1  | 1 | 1       | 0  | 0  | 0  |

| 0 | 1     | 0  | 0 | 0       | 1  | 0  | 0  |

| 0 | 1     | 0  | 1 | 0       | 0  | 0  | 0  |

| 0 | 1     | 1  | 0 | 0       | 1  | 0  | 0  |

| 0 | 1     | 1  | 1 | 0       | 0  | 0  | 0  |

| 1 | 0     | 0  | 0 | 0       | 0  | 0  | 0  |

| 1 | 0     | 0  | 1 | 0       | 0  | 1  | 0  |

| 1 | 0     | 1  | 0 | 0       | 0  | 0  | 1  |

| 1 | 0     | 1  | 1 | 0       | 0  | 1  | 0  |

| 1 | 1     | 0  | 0 | 0       | 0  | 0  | 0  |

| 1 | 1     | 0  | 1 | 0       | 0  | 1  | 0  |

| 1 | 1     | 1  | 0 | 0       | 0  | 0  | 1  |

| 1 | 1     | 1  | 1 | 0       | 0  | 1  | 0  |

Compare the output results in Truth Table 2 with Truth Table 1. What is your conclusion?

| The output results in Truth Table 2 with Truth Table 1 is the same. This is because X |

|---------------------------------------------------------------------------------------|

| is don't care which can be value 1 or 0. So in the Truth Table 2 the input same with  |

| Truth Table 1 that is don't care condition we also can ignore it.                     |

|                                                                                       |

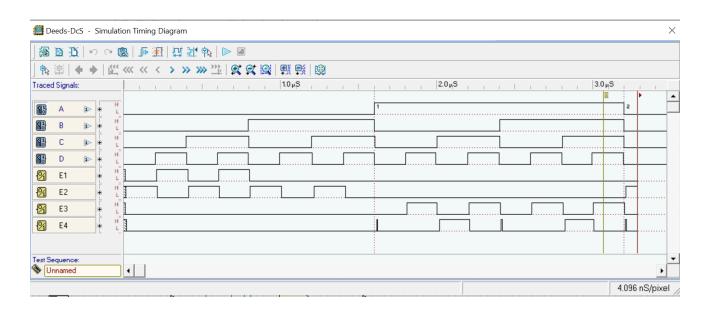

### b) Timing Diagram

Explain some analysis values based on your timing diagram:

When input D is high and other inputs are low or input C and D is high and other inputs are low, output E1 is high. When all the inputs are low or input B and C is high and the other inputs are low or input B or input C is high and the other inputs are low, output E2 is high. When input A and D is high and the other inputs are low or input A, C and D are high and the input B are low or when input A, B and D are high and input C is low or all the inputs are high, output E3 is high. When inputs A and C are high and the other inputs are low or input A, B and C are high and input D is low, output E4 is high.

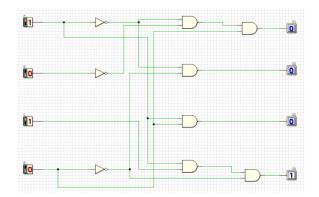

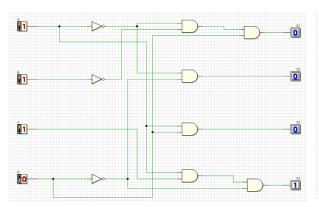

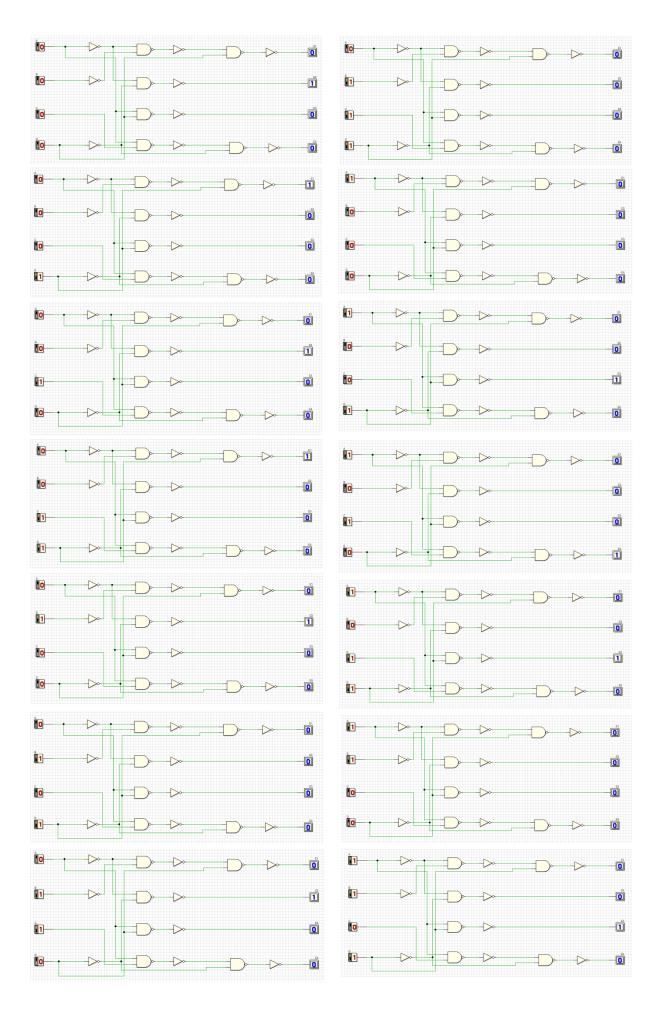

Using dual symbol concept, convert your circuit in step (3) to NAND gates only. Use Deeds Simulator.

- 6. Simulate the Deeds circuit in step (5):

- a) Update Truth Table 3 based on the simulation result.

Truth Table 3

|   | INPU' | ΓS |   | OUTPUTS |    |    |    |

|---|-------|----|---|---------|----|----|----|

| A | В     | C  | D | E1      | E2 | E3 | E4 |

| 0 | 0     | 0  | 0 | 0       | 1  | 0  | 0  |

| 0 | 0     | 0  | 1 | 1       | 0  | 0  | 0  |

| 0 | 0     | 1  | 0 | 0       | 1  | 0  | 0  |

| 0 | 0     | 1  | 1 | 1       | 0  | 0  | 0  |

| 0 | 1     | 0  | 0 | 0       | 1  | 0  | 0  |

| 0 | 1     | 0  | 1 | 0       | 0  | 0  | 0  |

| 0 | 1     | 1  | 0 | 0       | 1  | 0  | 0  |

| 0 | 1     | 1  | 1 | 0       | 0  | 0  | 0  |

| 1 | 0     | 0  | 0 | 0       | 0  | 0  | 0  |

| 1 | 0     | 0  | 1 | 0       | 0  | 1  | 0  |

| 1 | 0     | 1  | 0 | 0       | 0  | 0  | 1  |

| 1 | 0     | 1  | 1 | 0       | 0  | 1  | 0  |

| 1 | 1     | 0  | 0 | 0       | 0  | 0  | 0  |

| 1 | 1     | 0  | 1 | 0       | 0  | 1  | 0  |

| 1 | 1     | 1  | 0 | 0       | 0  | 0  | 1  |

| 1 | 1     | 1  | 1 | 0       | 0  | 1  | 0  |

| Compare the output results in Truth Table 3 with Truth Table 2. What is your conclusion? |

|------------------------------------------------------------------------------------------|

| NAND gate is the universal gate which can perform basic gate of AND gate                 |

| and inverter.                                                                            |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

### b) Timing Diagram

Explain some analysis values based on your timing diagram:

When input D is high and other inputs are low or input C and D is high and other inputs are low, output E1 is high. When all the inputs are low or input B and C is high and the other inputs are low or input B or input C is high and the other inputs are low, output E2 is high. When input A and D is high and the other inputs are low or input A, C and D are high and the input B are low or when input A, B and D are high and input C is low or all the inputs are high, output E3 is high. When inputs A and C are high and the other inputs are low or input A, B and C are high and input D is low, output E4 is high.