#### SCSR1013 DIGITAL LOGIC

MODULE 1: INTRODUCTORY CONCEPTS

2019/2020-1

**FACULTY OF COMPUTING**

www.utm.my

## Digital and Analog Quantities

#### **CONTENTS**

עש.utm.my

## MODULE 1: DIGITAL LOGIC OVERVIEW

Digital and Analog Quantities

Binary Digits, Logic Levels and Digital Waveform

Introduction to Logic Operations

Overview of Logic Functions

Fixed-Function IC

Programmable Logic Devices (PLD)

2

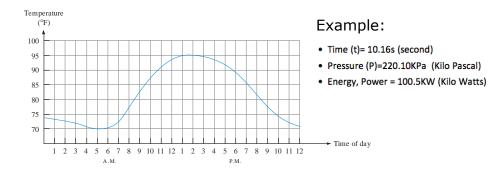

#### Analog quantities

- Most natural quantities that we see are analog and vary continuously.

- Analog systems can generally handle higher power than digital systems.

#### Digital quantities

#### Example:

- Band Width (BW) = 1Mbps (Mega Bits Per Second)

- Storage RAM = 512MB (Mega Byte)

- Hard Disk = 160GB (Giga Byte)

Digital systems can process, store, and transmit data more efficiently but can only assign discrete values (discontinuous) to each point.

#### Analog

- Use base 10 (decimal)

- Represented by 10 different level:

0, 1, 2, 3, 4, 5, 6, 7, 8, and 9.

- Analog system: A combination of devices that manipulate values represented in analog form

Resource: Floyd, Digital Fundamentals, 10th Edition

Temperature

100

95

5

6

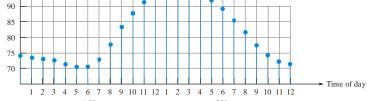

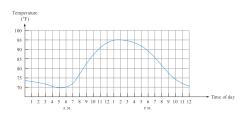

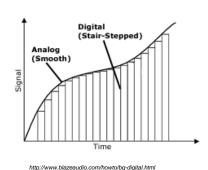

Analog vs Digital

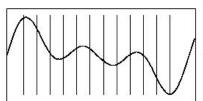

#### Example of sampling analogto-digital (frequency at least 2 times higher than analog)

ORIGINAL ANALOG

SIGNAL

DIGITAL

ANALYSIS OF

SIGNAL

DIGITAL

ASSIGNMENTS OF

SIGNAL

DIGITAL

ASSIGNAL

DIGITAL

ASSIGNAL

POPSIGNAL

http://www.geardiary.com/2011/04/01/music-diary-notes-the-brave-newworld-of-digital-music/digital\_sampling/

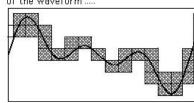

lower sample rates take fewer snapshots of the waveform ....

resulting in a rough recreation of the waveform.

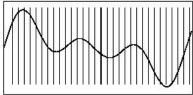

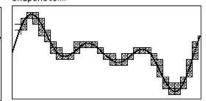

faster sample rates take more snapshots....

resulting in a smoother and more detailed recreation of the waveform.

http://musicandcomputers306.blogspot.com/2010/10/waveforms-ad-conversion-sampling.html

**Answer**

Resource: Google searched

(d)

9

Resource: Google searched

10

Example: Analog systems

Example: Digital systems

Resource: Google searched Resource: Google searched

#### **Digital**

- Digital technology is relatively new compared to analog technology, but a lot of analog systems has been changed to a digital systems, Examples:

- Computers

- Manufacturing systems

- Medical Science

- Transportation

- Entertainment

- **Telecommunications**

\*DSL-2320B (ADSL Modem)

**Exercise:** Match the picture to which digital

application system it belong to.

(e)

intel

(a)

- (a) Computers

- (b) Manufacturing systems

- (c) Medical Science

- (d) Transportation

- (e) Entertainment

- (f) Telecommunications

http://www.tvjuneau.com/images/HDTV-Resolutions\_Full.jpg

Resource: http://www.wirelessnetworkproducts.com/dsl-2320b.aspx

13

15

Resource: http://www.wirelessnetworkproducts.com/dsl-2320b.aspx

**Digital**

#### The Digital Advantages

- Ease of design

- Ease of storage

- Accuracy and precision are easier to maintain

- Programmable operation

- Less affected by noise

- Ease of fabrication on IC chips

- ☐ Thus, the digital systems is more efficient and reliable for:

- Data Processing

- Data Transmission

- Data Storage

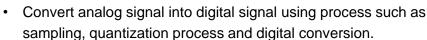

#### Digital Disadvantages

Greater bandwidth

Sampling error

Sampling Error (Quantization Error): is derived from Analog to Digital Conversion Process:

Bit 0 and 1

Compatibility with existing analog systems

Sampling & Quantization

Short product half life

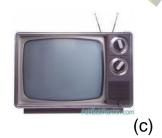

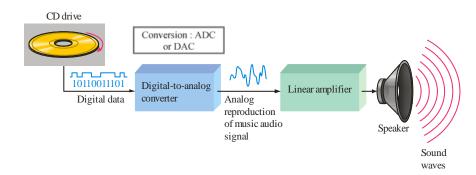

#### Analog and Digital Systems

- Many systems use a mix of analog and digital electronics to take advantage of each technology.

- A typical CD player accepts digital data from the CD drive and converts it to an analog signal for amplification.

Resource: Floyd, Digital Fundamentals, 10th Edition

18

## **Hybrid System**

- The audio CD is a typical hybrid (Analog & Digital) system.

- · Analog sound is converted into analog voltage using a microphone.

- · Analog voltage is changed into digital through an ADC in the recorder.

- Digital information is stored on the CD.

- At playback the digital information is changed into analog by a DAC in the CD player.

- The analog voltage is amplified and used to drive a speaker that produces the original analog sound.

- Convert digital sound (CD) to analog

- Process (amplify) the analog information

- Convert the analog signal to sound

Resource: Floyd, Digital Fundamentals, 10th Edition

HIGH SPEED Converters

#### **Conversion:**

#### **Analog to Digital Converter (ADC):**

Error will occur during the sampling and quantization, hence loss of information can happen.

#### Digital to Analog Converter (DAC):

- · Needed if the speaker is using analog system.

- Need to convert the digital data to analog signal in order for the speaker works properly and the sound can heard by human.

www.utm.mu

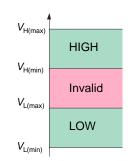

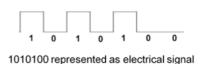

# Digits, Logic Levels and Digital Waveform

Digital electronics uses circuits that have two states, which are represented by two different voltage levels:

- HIGH (bit 1)

- LOW (bit 0)

A bit can have the value of either a 0 or a 1, depending on if the voltage is **HIGH** or **LOW**.

Resource: Floyd, Digital Fundamentals, 10th Edition

22

- A positive going pulse is one that goes from a normally LOW logic level to a HIGH level and then back again.

- Digital waveforms are made up of a series of pulses.

(a) Positive-going pulse

## Positive Logic (active high)

High =

$$I$$

(Bit  $I$ )

Low =  $0$  (Bit  $0$ )

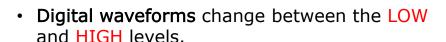

#### **Digital Waveforms**

Symbols to show the input state of "active high" and "active low":

"active high"

"active low"

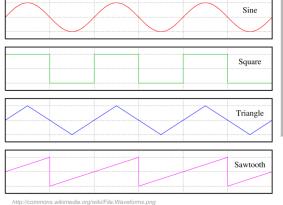

#### • Two type of squarewave

Periodic

· The signal keep on repeating after a period of time

Non-Periodic / Aperiodic

· Doesn't have a period

25

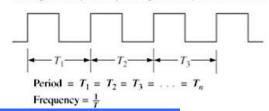

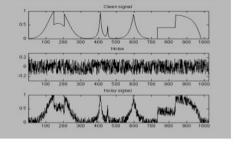

#### Periodic signal

#### Aperiodic signal

#### **Periodic Signal Parameter**

☐ Frequency (f) is the rate at which the signal repeat itself at a fixed interval. Is measured in cycles per second or Hertz (Hz)

$f = \frac{1}{T}$  Hz

☐ Period (T) is the time from the edge of one pulse to the corresponding edge of the next pulse. Is measured in second

$$T = \frac{1}{f}$$

seconds

#### **■** Example:

■ clock frequency: f = 100Hz, so, period: T = 1/100Hz = 0.01s = 10x 10<sup>-3</sup> = 10 ms

> $s \rightarrow ms (x 10^3)$  $ms \rightarrow s (x 10^{-3})$

#### Some examples of periodic signal display on the oscilloscope:

(a) Square waveform

(b) Sinusoid waveform

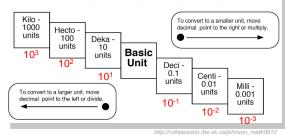

#### Metric Conversion Chart

#### **Unit Conversion**

- Kilo (K)= 10<sup>3</sup>

- Mega (M)= 10<sup>6</sup>

- Giga (G)= 10<sup>9</sup>

- Tera (T)=  $10^{12}$

- Mili (m)= 10<sup>-3</sup>

- Micro ( $\mu$ ) = 10<sup>-6</sup>

- Nano (n)= 10-9

- Piko (p) =  $10^{-12}$

29

30

- Mili (m)= 10<sup>-3</sup>

- Micro ( $\mu$ ) = 10-6

- Nano (n)= 10-9

- Piko (p) =  $10^{-12}$

Exercise 1.1: Calculate the frequency of signals if time period are given as the following:

Example:

$$f = 100KHz$$

, So  $T = 1/f$

$= 1/(100*10^3$ Hz)

$= 0.01*10^{-3} s$

= 0.01 ms

$= 10 \mu s$

$$= (0.01 * 10^{-3}) \text{ s x } 10^{6}$$

$$= (0.01 * 10^{-3+6}) \text{ us}$$

$= (0.01 * 10^3) \mu s$

$= 10 \mu s$

a)  $10ms = ____Hz$

b)  $100 ms = _KHz$

c)  $100ns = ____MHz$

d)  $1000ps = ____GHz$

$= (0.01 * 10^{-3}) \text{ s x } 10^{3}$  $= (0.01 * 10^{-3+3}) \text{ ms}$

$= (0.01 * 10^{313}) \text{ ms}$ =  $(0.01 * 10^{0}) \text{ ms}$ = 0.01 ms

- a)  $1000KHz = ____ms$

- b) 100MHz = ns

- c) 1000*GHz* = \_\_\_\_\_*ps*

- d) 100*THz* = \_\_\_\_*ps*

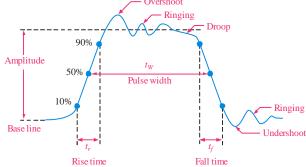

#### Pulse Definition

- Pulse is a rapid, transient change in the amplitude of a signal from a baseline value to a higher or lower value, followed by a rapid return to the baseline value.

- Pulse width  $(t_w)$ : A measure of the duration of the pulse.

• Rise time and fall time is a measure of how fast the pulse change.

Overshoot

Resource: Floyd, Digital Fundamentals, 10th Edition

34

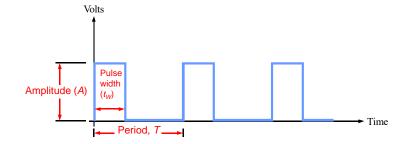

#### Repetitive Pulse Waveform

- In addition to frequency and period, repetitive pulse waveforms are described by the amplitude (A), pulse width (t<sub>W</sub>) and duty cycle.

- Duty cycle is the ratio of t<sub>W</sub> to T.

#### **Duty Cycle**

□ Duty cycle is the fraction of time that a system is in an "active" state (operated), defined as

Duty cycle =

$$(t_w/T)100\%$$

**Example**: a periodic digital waveform has a pulse width  $(t_w)$  1ms and period time (T) 10ms, calculate duty cycle?

Duty cycle = 1ms/10ms \* 100% = 10%

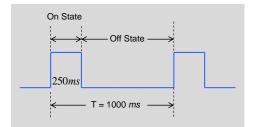

Exercise 1.3: Given the duration or period of a system is 1000ms, determine the *on state* and *off state* of the system that operate with the ratio of duty cycle is 25%. Show your works.

Solution 1.3:

Duty cycle → on state

$$= 25\% \ \ 1000ms = \frac{25}{100} \ \ 1000ms = \frac{1}{4} \ \ 1000ms = 250ms$$

Off state : = 1000ms - 250ms = 750ms

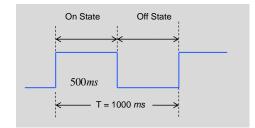

Exercise 1.4: Given the duration or period of a system is 1000ms, determine the *on state* and *off state* of the system that operate with the ratio of duty cycle is 50%. Show your works.

Solution 1.4:

Duty cycle → on state

$$= 50\% \ 1000ms = \frac{50}{100} \ 1000ms = \frac{1}{2} \ 1000ms = 500ms$$

Off state : = 1000ms - 500ms = 500ms

(module: page 18) 37 (module: page 18) 38

Exercise 1.5: Given the *duty cycles* of a system is 40% for a duration of a system is 500ms.

- a) Calculate the pulse width of the system.

- b) Determine the *off state* of the system that operate with the ratio of duty cycle.

Show your works.

Solution 1.5:

a)

$$DutyCycle = (\frac{t_W}{T})100$$

$$40 = (\frac{t_W}{500})100$$

$$t_W = \frac{40(500)}{100} = 200s$$

b)

$$Period = 500ms$$

$OnState = t_W = 200ms$

$\searrow 500 - 200 = 300ms$

39

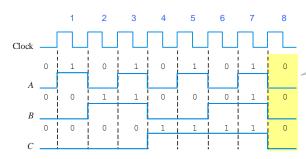

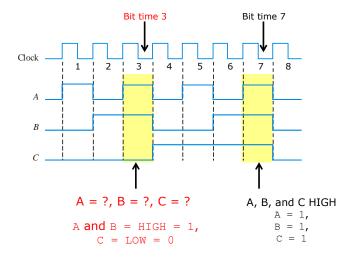

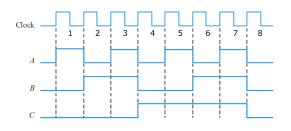

A timing diagram is used to show the relationship between two or more digital waveforms,

A diagram like this can be observed directly on a logic analyzer.

At time 8, all A, B, and C LOW

Timing diagram

#### **Example: Timing Diagram**

#### **Example: Timing Diagram**

| Clock | Input |   | Output |  |

|-------|-------|---|--------|--|

| (↑)   | Α     | В | С      |  |

| 1     | 1     | 0 | 0      |  |

| 2     | 0     | 1 | 0      |  |

| 3     | 1     | 1 | 0      |  |

| 4     | 0     | 0 | 1      |  |

| 5     | 1     | 0 | 1      |  |

| 6     | 0     | 1 | 1      |  |

| 7     | 1     | 1 | 1      |  |

| 8     | 0     | 0 | 0      |  |

**Exercise:** Complete the truth table.

Resource: Floyd, Digital Fundamentals, 10th Edition

41

Resource: Floyd, Digital Fundamentals, 10th Edition

42

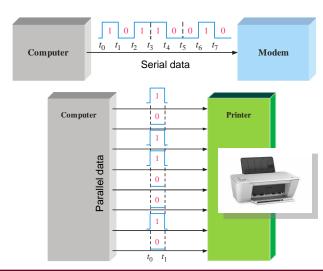

#### **Data Transfer**

աաա.սւm.my

Data can be transmitted by either **serial** transfer or **parallel** transfer.

Introduction to Logic Operations

#### Basic logic function

True only if **all** input conditions are true.

True only if **one or more** input conditions are true.

NOT

Indicates the *opposite* condition (inverter).

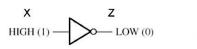

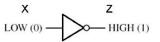

#### **Logic Gates: NOT**

NOT operation

Truth table shows the relationship between output and the input.

Truth Table for NOT

| Х | Z |

|---|---|

| 0 | 1 |

| 1 | 0 |

7404 IC six inverters

Resource: Floyd, Digital Fundamentals, 10th Edition

45

\_\_\_\_\_

46

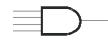

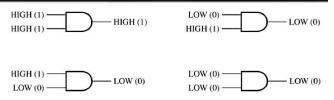

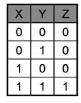

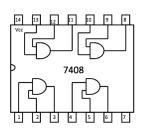

#### **Logic Gates: AND**

#### AND operation

Truth Table AND

7408 IC four (Quad) AND gates

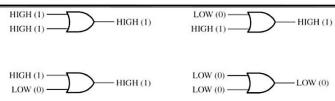

#### **Logic Gates: OR**

#### OR operation

|                | X | Υ | Z |

|----------------|---|---|---|

|                | 0 | 0 | 0 |

| Truth Table OR | 0 | 1 | 1 |

|                | 1 | 0 | 1 |

|                | 1 | 1 | 1 |

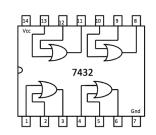

7432 integrated circuit provides four (Quad) two-inputs OR gates

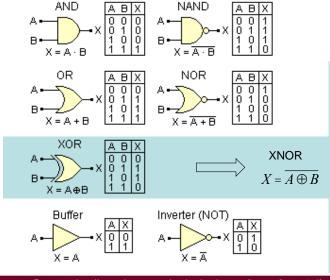

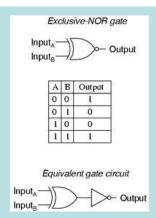

#### Logic Gates:

Summary

www.utm.my

Overview of Logic Functions

Resource: http://www.chem.uoa.gr/applets/appletgates/Images/Image1.gif

49

50

#### **Basic Logic Functions**

- Any digital systems has one or more of the following function.

- ☐ This functions are built from the basic gates.

- · Comparison Function

- · Arithmetic Functions

- Code conversion function

- Encoding function

- · Decoding function

- Data selection function

- Data storage function

- · Counting function

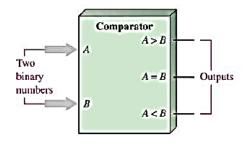

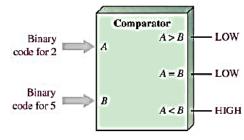

#### **Comparison Function**

(a) Basic magnitude comparator

(b) Example: A is less than B (2 < 5) as indicated by the HIGH output (A < B)

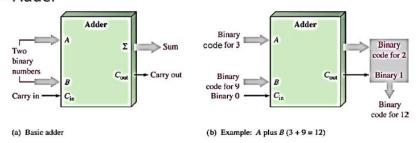

#### **Arithmetic Functions**

Adder

- Subtractor

- Multiplier

- Division

All the other arithmetic operations can be derived from adder:

- ☐ Subtraction is and addition of negative number such as A−B = A+(-B)

- ☐ Multiplication is a repeated addition such as A\*3=A+A+A

- □ Division is a repeated subtraction which is a repeated addition such as 6/3=6-3-3=6+(-3)+-(3)

- subtract until the remainder = 0

- total number of subtraction = 2 which is the answer

Resource: Floyd, Digital Fundamentals, 10th Edition

53

54

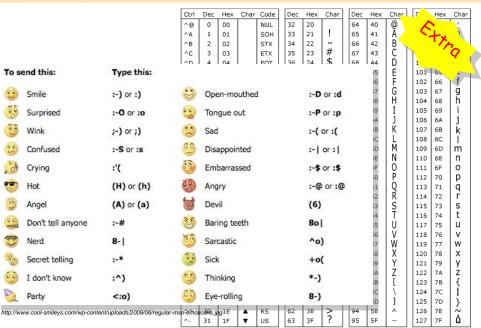

#### **Code Conversion Function**

- A code is a set of bits arranged in a unique pattern and used to represent specified information.

- Examples : BCD, ASCII

- The usage of codes allow a faster and more efficient data processing.

http://depositphotos.com/2746252/stock-illustration-Arabic-alphabet.htm

<sup>\*</sup> ASCII code 127 has the code DEL. Under MS-DOS, this code has the same effect as ASCII 8 (BS)

The DEL code can be generated by the CTRL + BKSP key

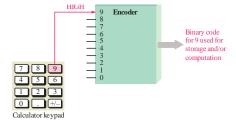

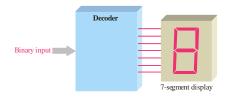

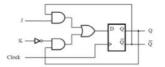

#### **Encoding & Decoding Function**

The encoding function

The decoding function

Resource: Floyd, Digital Fundamentals, 10th Edition

58

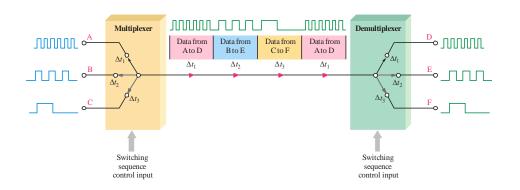

## Data Selection Function: MUX & DeMUX

#### Problem:

Many inputs (e.g. A, B and C) wanted to use a single transmission line for their data transmission. How to make sure the data is transferred in a proper manner (issue of cost, synchronization, conflict, crash, loss?)

Source (A, B, C) and Destination (D, E, F)  $A \rightarrow D$ .  $B \rightarrow E$ .  $C \rightarrow F$

Solution:

Select and permit only one device can use the line and transfer its data at one time.

Data in the transmission line would be arranged as A, B, C

DEMUX: select and route the data to their originate destination  $A \rightarrow D, B \rightarrow E, C \rightarrow F$

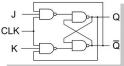

#### **Data Storage Function**

Flip-flop

- Flip-flop stores a 1 or 0 only

- Registers

- Formed by combining several flip-flops

- ∘ 8-bit register → from 8 flip-flops

- Semiconductor Memories

- e.g. RAM, ROM, Flash

- Magnetic/Optical Memories

- ∘ For mass storage → e.g. hard disk, tape, DVD, Blu-Ray

61

Memories

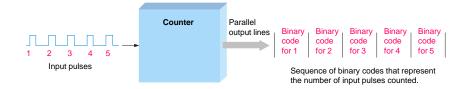

### Counting Function

Counter

#### Examples:

- Traffic light

- Washing machine

- Vending machine

- Xerox machine

- ATM machine

- etc.

- To count the occurrence at the input.

- to initiate a controller after a certain count (period).

Resource: Floyd, Digital Fundamentals, 10th Edition

62

#### UTIM UNIVERSITI TEKNOLOGI MALAYSIA

աաա.utm.my

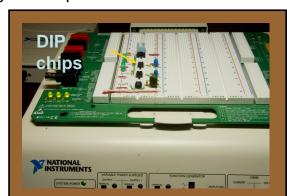

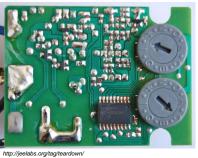

Fixed-Function Integrated Circuit (IC) An example of laboratory prototyping is shown. The circuit is wired using DIP chips and tested.

In this case, testing can be done by a computer connected to the system.

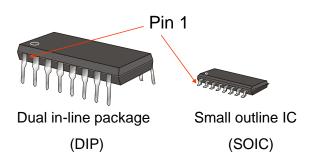

(Dual In-line Package)

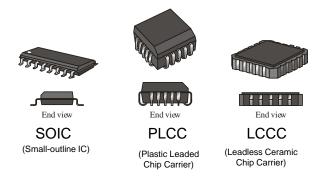

#### **IC Packages**

DIP chips and surface mount chips

Other surface mount technology (SMT) packages:

Resource: Floyd, Digital Fundamentals, 10th Edition

65

Resource: Floyd, Digital Fundamentals, 10th Edition

66

## IC and conventional **through-hole** technology

ttp://aa7ee.wordpress.com/page/4/

Printed Circuit Board ( PCB)

#### **Surface Mount PCB**

https://neuromorphs.net/ws2007/wiki/si

http://www.pcb-manufacturers.co.uk/pcb-production-examples-c.htm

67

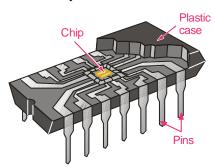

Integrated circuit

#### Cutaway view of DIP (<u>Dual-In-line Pins</u>) chip:

IC Packaging: Why we need packaging?

- To protect the IC (circuit)

- Have a pin system so that can connect to other circuit

Resource: Floyd, Digital Fundamentals, 10th Edition

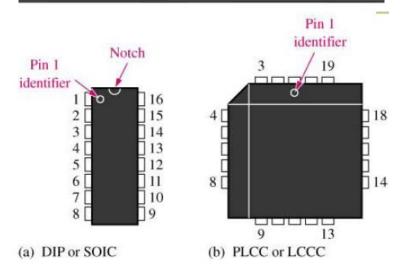

#### **Pin Numbering**

http://www.rkonlinestore.co.uk/556-dual-timer-ic-16pin-dip-pack-of-4-391-p.asp

70

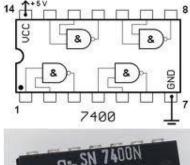

http://electroschematics.com/6529/7400-datashee

## Complexity Classifications for Fixed-Function ICs

- ☐ Small-scale integration (SSI) have up to 12 gates on a single chip

- ☐ Medium-scale integration (MSI) have from 12-99 gates on a single chip

- □ Large-scale integration (LSI) have from 100-9999 gates on a single chip

- □ Very large-scale integration (VLSI) have from 10,000-99,999 gates on a single chip

- ☐ Ultra large-scale integration (ULSI)

have from 100,000 and greater equivalent gates on

a single chip

Module 1

69

http://www.visual6502.org/images/263P/S SI\_263P\_8404\_chip1\_package\_top.jpg

http://www.nysemagazine.com/lsicorp

71

#### **Integrated Circuit Technologies**

#### Some examples of IC technologies:

- TTL (Transistor-transistor Logic)

- ECL (Emitter-Coupled Logic)

- CMOS (Complementary Metal-Oxide-Semiconductor)

- NMOS (N-Type Metal–Oxide–Semiconductor)

- BiCMOS (Bipolar and Metal-Oxide-Semiconductor)

ttp://www.creativeplanetnetwork.com/dcp/news/cm

## **Programmable Logic Devices (PLD)**

#### Overview of PLD

#### □ Fixed function

■ A specific logic function is contained in the IC (hardwired) and can never be changed.

#### □ PLD

- Logic function programmed by the user.

- ■Some, can be reprogrammed many times.

- Advantage

- ■More logic circuit can be 'stuffed' into much smaller

- ■Certain PLD, design can be changed without rewiring or replacing components.

- ■Can be implemented faster once the required programming language is mastered.

73 74

#### Types of PLD

3 major types (SPLD, CPLD, FPGA)

- 1. Simple Programmable Logic Devices (SPLD)

- Can replace several fixed-function SSI or MSI

- First type available

- A few categories

- PAL (programmable Array Logic)

- GAL (Generic Array Logic)

- PLA (Programmable Logic Array)

- PROM (Programmable Read-Only memory)

#### Types of PLD: CPLD

- 2. Complex Programmable Logic Devices (CPLD)

- Much higher capacity than SPLD (2-64 SPLD)

- More complex logic circuits can be programmed

- Typically in 44 160 pin package

(b) 128-pin PQFP package

#### Types of PLD: FPGA

- 3. Field-Programmable Gate Arrays (FPGA)

- □ Different internal organization than SPLD and CPLD

- □ Greatest logic capacity

- Consist of 64- thousands logic block (logic gate groups)

- Classes

- Fine grain (smaller logic block)

- Coarse grain (large logic block)

77

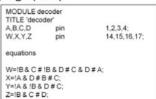

Logic circuit entered using 2 basic method

· schematic diagram

**PLD Programming**

- Text-based entry (language based entry)

- · Using Hardware Description Language (HDL)

- · Eg . ABEL, CUPL, WinCUPL

- Becoming widely used especially for CPLD and FPGA

- VHDL

- Verilog

Resource: http://upload.wikimedia.org/wikipedia/commons/thumb/f/fa/ Altera\_StratixIVGX\_FPGA.jpg/300px-Altera\_StratixIVGX\_FPGA.jpg