#### **Objectives**:

- To provide a more detailed look at machine instruction sets.

- To look at different instruction types and operand types, and how instructions access data in memory.

- To understanding how instruction sets are designed and how their function can help to understand the more intricate details of the architecture of the machine itself.

- 4.1 Introduction

- 4.2 Machine Instruction Characteristics

- 4.3 Types of Operands

- 4.4 Addressing Modes

- 4.5 Instruction Formats

- 4.6 Summary

4.1 Introduction

### 4.2 Machine Instruction Characteristics

- 4.3 Types of Operands

- 4.4 Addressing Modes

- 4.5 Instruction Formats

- 4.6 Summary

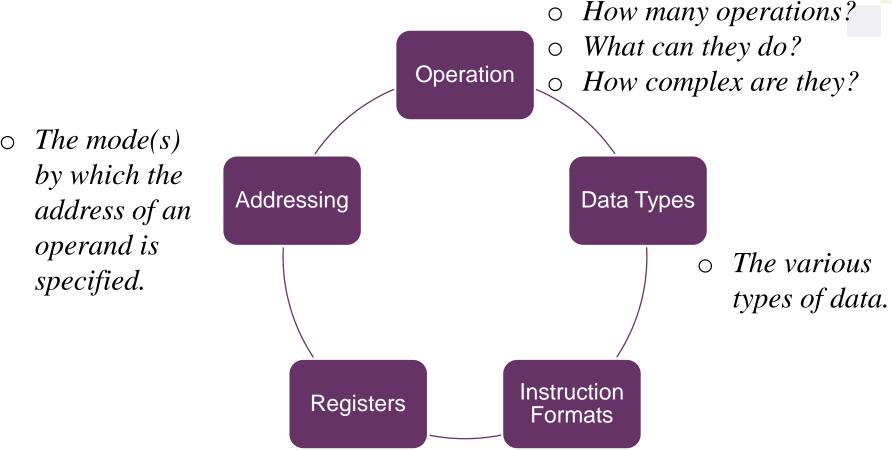

- Elements of a Machine Instruction

- Instruction Representation

- Instruction Types

- Number of Addresses

- Instruction Set Design

#### Let's recall

■ Four common instruction formats:

(a) Zero-address instruction.

OPCODE

(b) One-address instruction

OPCODE ADDRESS

(c) Two-address instruction.

OPCODE ADDRESS1 ADDRESS2

(d) Three-address instruction.

OPCODE ADDR1 ADDR2 ADDR3

### **Example**: Program to execute $Y = \frac{A - B}{C + (D \times E)}$

$$Y = \frac{A - B}{C + (D \times E)}$$

4 instructions

| Instru | ction   | Comment                   |  |  |

|--------|---------|---------------------------|--|--|

| SUB    | Y, A, B | $Y \leftarrow A - B$      |  |  |

| MPY    | T, D, E | $T \leftarrow D \times E$ |  |  |

ADD T, T, C  $T \leftarrow T + C$

Y, Y, T  $Y \leftarrow Y \div T$ DIV

(a) Three-address instructions

| Instruction | Comment                   |

|-------------|---------------------------|

| MOVE Y, A   | $Y \leftarrow A$          |

| SUB Y, B    | $Y \leftarrow Y - B$      |

| MOVE T, D   | $T \leftarrow D$          |

| MPY T, E    | $T \leftarrow T \times E$ |

| ADD T, C    | $T \leftarrow T + C$      |

| DIV Y, T    | $Y \leftarrow Y \div T$   |

(b) Two-address instructions

6 instructions

10 instructions

| <u>nstruc</u> | tion | Comment                     | ` / | lo-address<br>action |

|---------------|------|-----------------------------|-----|----------------------|

| OAD           | D    | $AC \leftarrow D$           |     |                      |

| <b>IPY</b>    | E    | $AC \leftarrow AC \times E$ |     |                      |

$AC \leftarrow AC + C$ ADD  $Y \leftarrow AC$ STOR Y

LOAD A  $AC \leftarrow A$

SUB  $AC \leftarrow AC - B$

DIV  $AC \leftarrow AC \div Y$

$Y \leftarrow AC$ STOR Y

(c) One-address instructions

8 instructions

PUSH C PUSH D PUSH E

**MUL**

**ADD**

**SUB**

DIV

POP

PUSH B PUSH A

Y

#### **How Many Addresses?**

Number of addresses per instruction is a basic design decision.

#### More addresses:

- More complex (powerful?) instructions.

- Fewer instructions per program.

- More registers:

- → Inter-register operations are quicker.

#### ■ Fewer addresses:

- Less complex (powerful?) instructions.

- More instructions per program.

- Faster fetch/execution of instructions.

### Instruction Set Design

- The design of an instruction set is very complex because it affects so many aspects of the computer system.

- The instruction set defines many of the functions performed by the processor.

- The instruction set is the programmer's means of <u>controlling</u> the processor. Thus, programmer <u>requirements</u> must be considered in designing the instruction set.

The most important of these fundamental design issues include the following:

- Number of CPU registers available.

- Which operations can be performed on which registers?

- Length of opcode field.

- Number of addresses.

- 4.1 Introduction

- 4.2 Machine Instruction Characteristics

- 4.3 Types of Operands

- 4.4 Addressing Modes

- 4.5 Instruction Formats

- 4.6 Summary

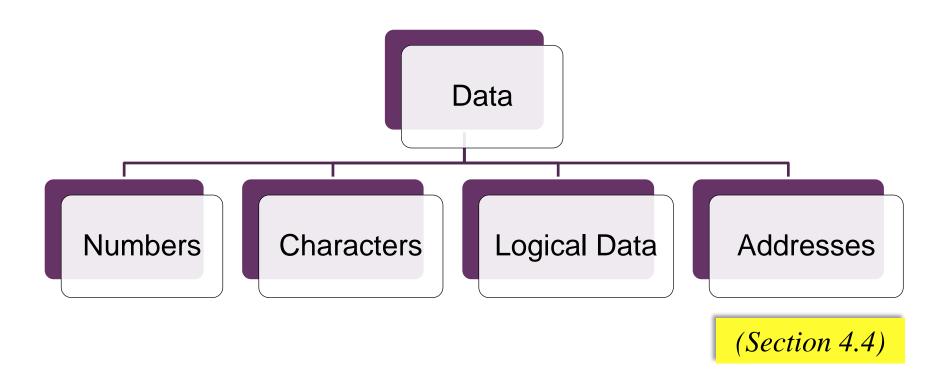

- Overview

- Numbers

- Characters

- Logical Data

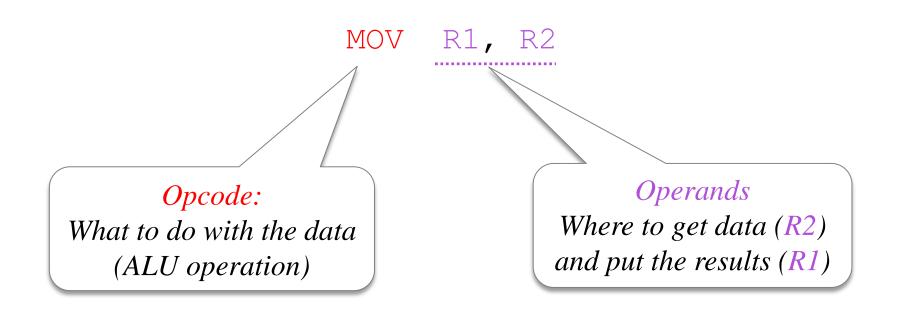

Assembly language built from two pieces:

- Machine instructions operate on data.

- The most important general categories of data:

#### Table: Type of operand for Pentium 4

| Туре                         | 1 Bit | 8 Bits | 16 Bits | 32 Bits | 64 Bits | 128 Bits |

|------------------------------|-------|--------|---------|---------|---------|----------|

| Bit                          |       |        |         |         |         |          |

| Signed integer               |       | ×      | X       | X       |         |          |

| Unsigned integer             |       | ×      | X       | X       |         |          |

| Binary coded decimal integer |       | ×      |         |         |         |          |

| Floating point               |       |        |         | X       | X       |          |

Single Precision

Double Precision

- All machine languages include numeric data types.

- An important distinction between numbers used in <u>ordinary</u> <u>mathematics</u> and numbers <u>stored in a computer</u> is that the latter are limited: (2 reasons)

- □ There is a limit to the magnitude of numbers representable on a machine.

- □ A limit to the <u>precision</u> of floating-point numbers.

- 3 types of numerical data:

- Binary integer or binary fixed point

- Binary floating point

- Decimal

#### Example 3a: x86 numerical data types.

(Unsigned integers)

■ The unsigned integers may be 16, 32, or 64 bits long.

| 7 0 | Byte unsigned integer       |

|-----|-----------------------------|

| 15  | Word unsigned integer       |

| 31  | Doubleword unsigned integer |

| 3   | Quadword unsigned integer   |

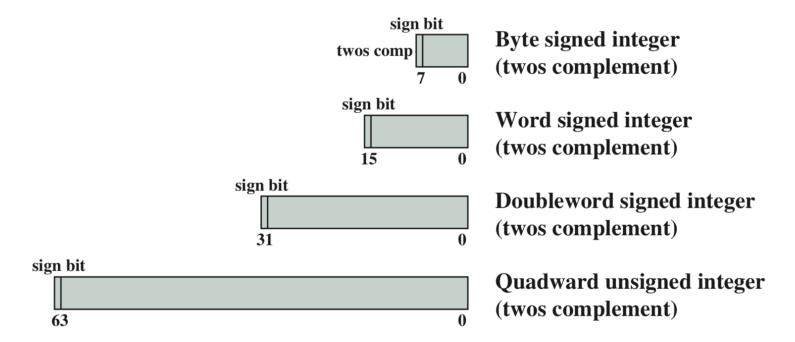

#### Example 3b: x86 numerical data types.

(Signed integers)

The signed integers are in two's complement representation and may be 16, 32, or 64 bits long.

#### Example 3c: x86 numerical data types.

(Signed integers)

■ The floating-point type actually refers to a set of types that are used by the floating-point unit and operated on by floating-point instructions → IEEE 754 standard.

- A common form of data is text or character strings.

- Today, the most commonly used character → United States as the American Standard Code for Information Interchange (ASCII).

- Another code used to encode characters is the *Extended Binary Coded Decimal Interchange Code* (EBCDIC); used on IBM mainframes.

- Normally, each word or other addressable unit (byte, halfword, and so on) is treated as a single unit of data → n-bit unit.

- When data are viewed this way, they are considered to be logical data.

- Two advantages to the bit-oriented view:

- ☐ Memory used efficiently to store an array of Boolean or binary data items for either values 1 (*true*) and 0 (*false*).

- □ Easy to manipulate the bits of a data item.

- 4.1 Introduction

- 4.2 Machine Instruction Characteristics

- 4.3 Types of Operands

#### 4.4 Addressing Modes

- 4.5 Instruction Formats

- 4.6 Summary

- Overview

- Immediate Addressing

- Direct Addressing

- Indirect Addressing

- Register Addressing

- Register Indirect Addressing

- Displacement Addressing

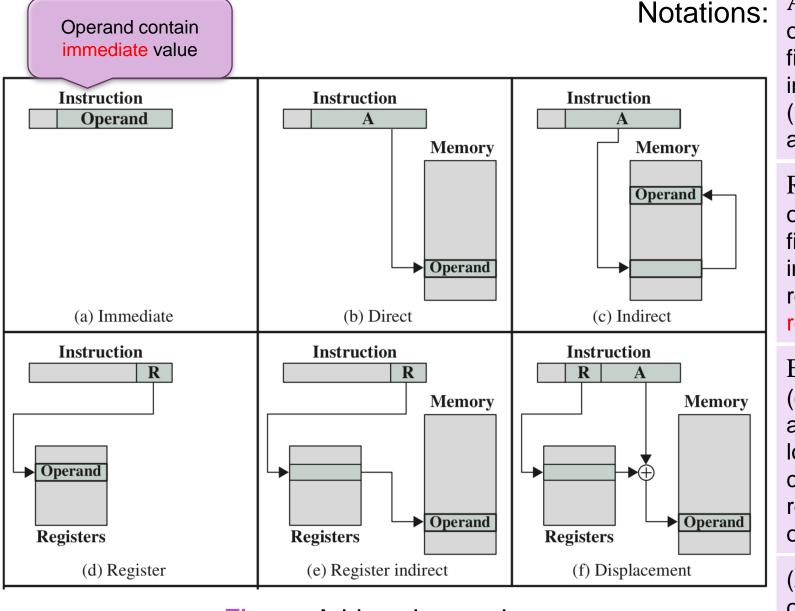

■ Two issues arise in specifying the <u>operands addresses</u> and <u>operations of instructions</u>:

How the address of an operand is specified?

How the bits of an instruction are organized?

■ A variety of addressing techniques has been employed to be able to reference a <u>large range</u> of locations in main memory or, for some systems, virtual memory.

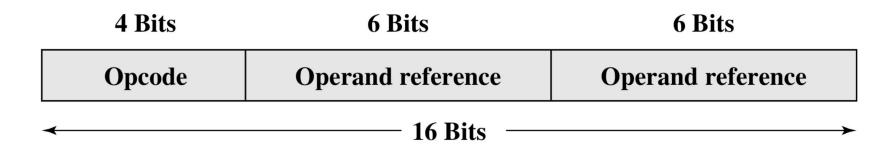

### Let's recall what we have learned so far about ISA

- Each instruction is represented by a <u>sequence of bits</u> that <u>divided into fields</u>, corresponding to the constituent elements of the instruction.

- Example of simple instruction format:

Table: The elements of a machine instruction.

| Elements                                |                           | Description                                                                                                 |                 |  |

|-----------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------|-----------------|--|

| Operation code                          | 0                         | Specifies the operation to be performed a                                                                   |                 |  |

| (Opcode)                                |                           | binary code (e.g., MOV, ADI                                                                                 | , SUB <b>).</b> |  |

| Source operand reference                | 0                         | The operation may involve one or more source operands, that is, operands that are inputs for the operation. |                 |  |

| Result operand reference (Destination). | 0                         | The operation may produce a result.                                                                         |                 |  |

| Next instruction reference              | 0                         | This tells the processor where to fetch the next instruction after the execution of this                    |                 |  |

|                                         | instruction is completed. |                                                                                                             | Invisible       |  |

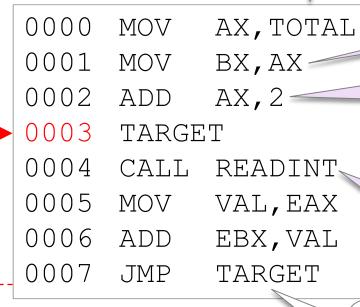

#### Example 1: Portion of an assembly language.

Addressing Mode

- Source and result operands (Destination) can be in one of four areas:

Section 4.4:

- Main or virtual memory :

Memory address for both must be supplied.

- Processor (CPU) registers: One or more registers that can be referenced by instructions.

- Immediate: The value of the operand is contained in the field in the instruction executed.

- I/O device Instruction specifies the I/O module and device for the operation

#### **Example 2**:

Operand: Memory

Current Ins.: 0000

Next Ins. : 0001

Current Ins.: 0007

Next Ins. : 0003

Operand: Register

Operand: Immediate value

Operand: From I/O

Next instruction is where TARGET is located = 0003

Figure: Addressing modes.

A = contents

of an address

field in

instruction

(memory

address)

R = contents of an address field in instruction that refers to a register.

EA = actual (effective) address of the location containing the referenced operand.

(X) = contents of memory location X or register X.

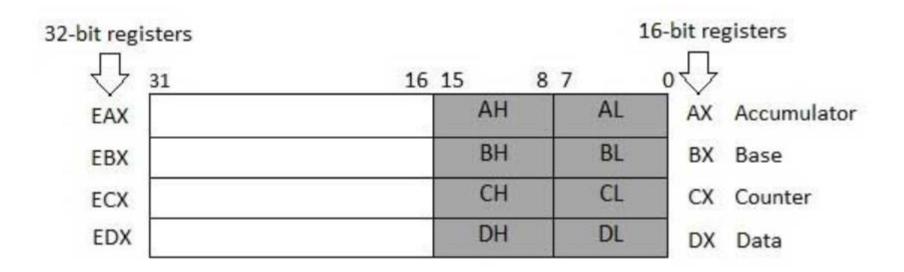

### A little bit about registers (further details in next module)

- Processor operations mostly involve processing data. This data can be stored in memory and accessed from thereon. However, reading data from and storing data into memory slows down the processor, as it involves complicated processes of sending the data request across the control bus and into the memory storage unit and getting the data through the same channel.

- To speed up the processor operations, the processor includes some internal memory storage locations, called registers

#### Registers

- General registers

- Data registers; EAX, EBX, ECX, EDX

- Pointer registers; EIP, ESP, EBP

- Index registers; ESI, EDI

- Control registers (flag); OF, DF, IF, TF, SF, ZF, AF, PF, CF

- Segment registers (specific areas defined in a program for containing data, code and stack)

- Code segment

- Data segment

- Stack segment

#### Let's recall

■ Data registers; EAX, EBX, ECX, EDX

Operand = A

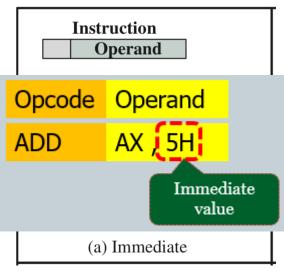

#### (a) Immediate Addressing

- The simplest form of addressing, in which the operand value is present in the instruction.

- Can defines and uses constant or set initial values of variables.

- Saving one memory or cache > No memory reference other than the instruction fetch is required, (faster).

The size of the number is restricted to the size of the address field.

$$EA = A$$

#### e.g. add EAX, A

- Look in memory at address A for operand

- Add contents of cell A to register EAX

Requires only one memory reference and no special calculation.

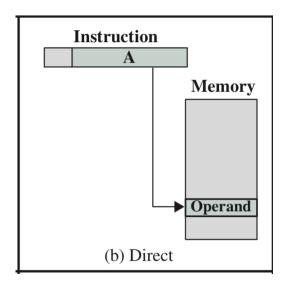

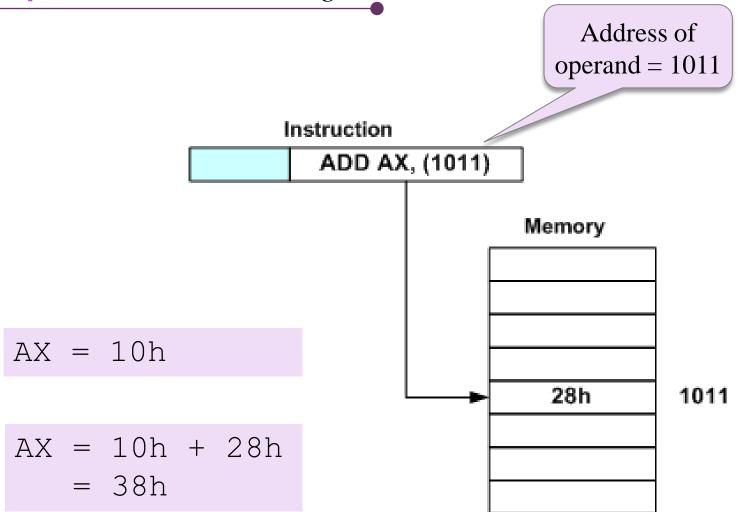

### (b) Direct Addressing

- The address field contains the Effective Address (EA) of the operand.

- EA=A=address field of (A)

- The address field refers to a main memory address

It provides only a limited address space.

#### **Example 4**: Direct addressing.

- Retype the next following coding in Example 5 12

- Then proceed with these 2 tasks:

- (A) Execute ; [Start Without Debugging ]

- (B) Debug ; F10

#### **Example 5**: Direct addressing.

al = 10h bx = 2210hecx = 00000123h

```

.data

```

val1 byte 10h array1 word 2210h, 11h array2 dword 123h, 234h

.code

```

main PROC

mov al,val1

mov bx,array1

mov ecx,array2

call dumpregs

exit

main ENDP

```

#### (DumpRegs)

EAX=7611ED10 EBX=7FFD2210 ECX=00000123 EDX=00401022 ESI=00000000 EDI=00000000 EBP=0012FF94 ESP=0012FF8C EIP=0040102D EFL=00000246 CF=0 SF=0 ZF=1 OF=0

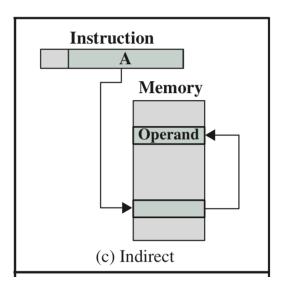

#### (c) Indirect Addressing

4

Memory cell pointed to by address field contains the address of the operand @ ( pointer to operand )

■ Solution for the limitation of the address range in *direct* addressing → to have the address field address of a word in memory, full-length address of the operand.

EA = (A)

Look in A, find address (A), and look there for operand.

No particular advantage.

Three or more memory references could be required to fetch an operand; slower.

the register in brackets must be incremented by a value that matches the array type  $\rightarrow$  1 for byte, 2 - word, 4 dword.

### **Example 6**: *Indirect addressing*.

bl 10h

0123h CX

00123456h edx =

0234h ax

### .data

array1 byte 10h array2 word 123h,234h array3 dword 123456h

.code

main PROC

MOV mov mov

mov call exit

Move the content of the memory where the first byte of arrayl is kept into

bl, [array1] cx, [array2] edx, [array3]

ax, [array2+2]

dumpreqs

main ENDP

### (DumpRegs)

EAX=00000234 EBX=00000010 ECX=00000123 EDX=00123456

EBP=0012FF94 ESP=0012FF8C ESI=00404004 EDI=00404008

EIP=0040104C EFL=00000246 CF=0 SF=0 ZF=1 0F=0

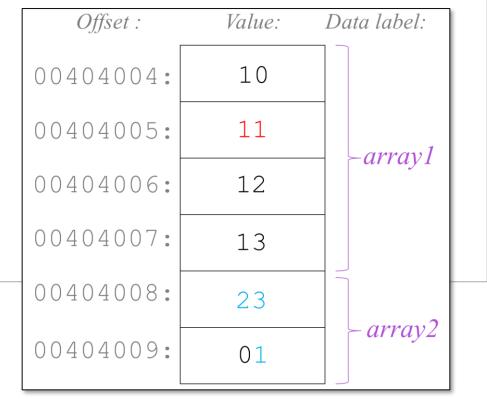

### Exercise 4.1:

.data

array1 byte 10h array2 word 123h,234h array3 dword 123456h

00404004:

Given three arrays with multiple initializer in assembly language program. Complete the following diagram by writing:

- (a) the offset for all memory. Assume the first offset is 00404004.

- (b) the value of the data stored using *Little Endian Order*.

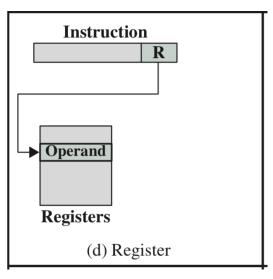

EA = R

No time consuming memory references needed

→ faster.

# (d) Register Addressing

- Similar to direct addressing, except the address field refers to a register rather than a main memory address.

- The programmer need to decide which values should remain in registers and which should be stored in main memory.

It has limited number of registers → provides a limited address space.

#### .data

.code

### **Example 7**: Register addressing.

```

eax = 000000000h

ebx = 00002000h

ecx = 00003000h

eax = 00002000h

eax = 00005000h

```

```

main

PROC

eax, 0

mov

ebx,2000h

mov

ecx, 3000h

mov

eax, ebx

mov

add

eax, ecx

call dumpregs

exit

main ENDP

```

### (DumpRegs)

EAX=00005000 EBX=00002000 ECX=00003000 EDX=00401005 ESI=00404004 EDI=00000000 EBP=0012FF94 ESP=0012FF8C EIP=00401028 EFL=00000206 CF=0 SF=0 ZF=0 OF=0

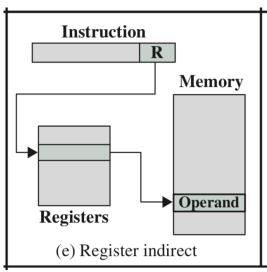

$$EA = (R)$$

# (e) Register Indirect Addressing

- Similar to *indirect addressing*.

- The <u>advantages</u> and <u>limitations</u> of <u>register indirect</u> addressing are basically the same as for <u>indirect</u> addressing.

Register indirect addressing uses one less memory reference than indirect addressing.

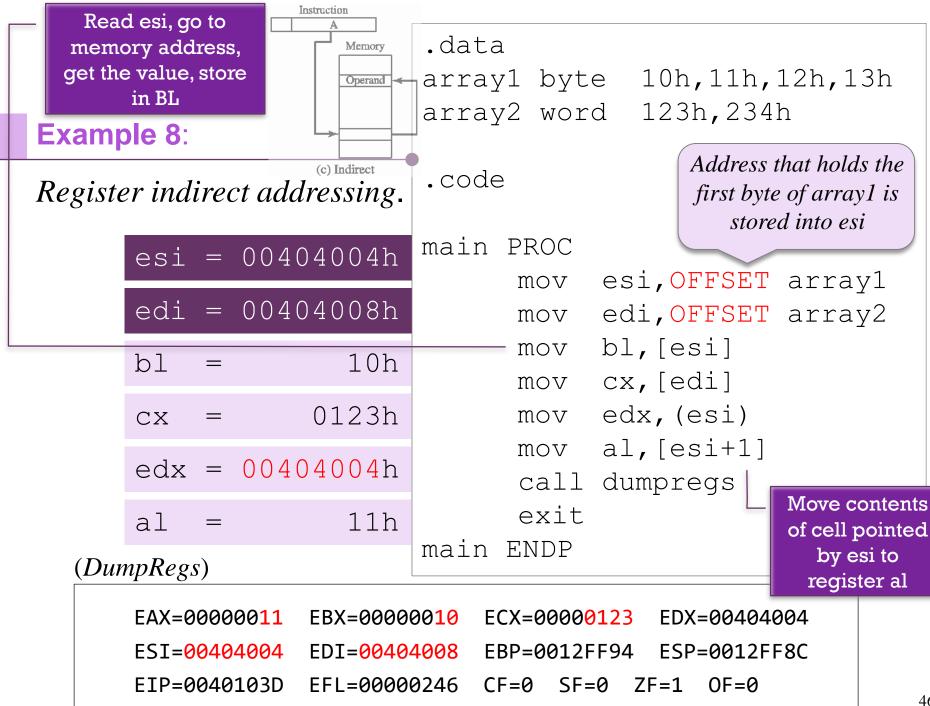

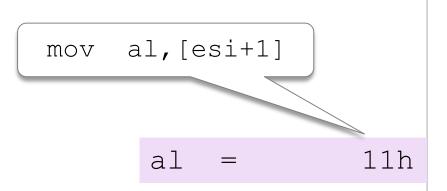

### **Example 8**:

### Register indirect addressing.

```

esi = 00404004h

edi = 00404008h

bl = 10h

cx = 0123h

edx = 00404004h

al = 11h

```

```

.data

array1 byte 10h,11h,12h,13h

array2 word 123h,234h

```

.code

Address of the data that stored in register.

```

PROC

main

esi, OFFSET array1

mov

edi, OFFSET array2

mov

bl, [esi]

mov

cx, [edi]

mov

edx, (esi)

mov

al, [esi+1]

mov

call

dumpreqs

exit

main ENDP

```

### (DumpRegs)

EAX=00000011 EBX=00000010 ECX=00000123 EDX=00404004 ESI=00404004 EDI=00404008 EBP=0012FF94 ESP=0012FF8C EIP=0040103D EFL=00000246 CF=0 SF=0 ZF=1 OF=0

array1 byte 10h,11h,12h,13h array2 word 123h,234h

### **Example 8**:

### Register indirect addressing.

$$esi = 00404004h$$

$edi = 00404008h$

.data

.code

### **Example 9**:

### Register indirect addressing.

ebx = 00404000h

dl 24h

00404001h ebx

cl 55h

#### main PROC

ebx, 404000h mov

dl, [ebx] mov

inc ebx

cl, [ebx] mov

dumpregs call

exit

main ENDP

### Offset: Value: 00404000:

00404001:

00404002: 88

24

55

### (DumpRegs)

ECX=00000055 EAX=00005000 EBX=00404001 EDX=00000024

ESI=00404000 EDI=00000000 EBP=0012FF94 ESP=0012FF8C

EIP=0040103D EFL=00000202 CF=0 SF=0 ZF=0 0F=0

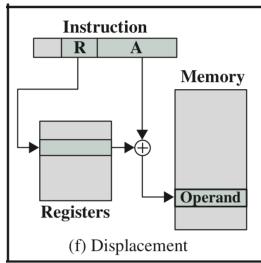

$$EA = A + (R)$$

3 common displacement addressing techniques:

Relative addressing

Base-Register addressing

Indexed addressing

- - A very powerful mode of addressing combines the capabilities of direct addressing and register indirect addressing.

- Address field hold two values:

- A = base value

- R = register that holds displacement (or vice versa)

# (f.1) Relative Addressing

Also called PC-relative addressing, the implicitly referenced register is the *Program Counter* (PC).

$$R = PC$$

$$EA = A + (PC)$$

■ The next instruction address (shown in PC) is added to the address field to produce the EA.

### Displacement Addressing.

(1) Relative addressing -(ve) because its 0000014 B9 0000000 mov ecx, 0 jumping backwards 0000019 0000000 mov edx, 0 BA000001E 0000000 В8 mov eax, 0 00000023 B9 00000004 mov eax, 4 00000028 L1: 00000028 661 8B 98 mov bx, array2[eax] 00000008 R PC = 3983 C0 02 000002F add eax, 2 Need to go to 00000032 E8 00000000 E call dumpregs LOOP L1

00000037 E2 EF

0000039 6A 00

exit PC = 39+000000000h push

L1 which is in 00000028

Destination = Target - Source

=L1-PC

= 28h - 39h

=-11h = EF

# 4

## (f.2) Base-Register Addressing

$$EA = A + R$$

- o A holds displacement.

- R holds pointer to base address.

- R may be explicit or implicit.

### Displacement Addressing.

(2) Base-register addressing

```

.data

dword 10h

count

array1 byte 10h,11h,12h,13h

array2 word 123h, 234h, 345h, 456h

array3 dword 123456h,

Base-index

addressing

.code

main PROC

mov esi, offset array1

mov ebx, 10h

mov ax, word ptr[ebx+esi]

add ebx, esi

mov cx, word ptr[ebx]

call dumpregs

exit

main ENDP

Base

addressing

```

Because AX and CX is a word size, then 2 bytes will be put in.

### Displacement Addressing.

(b) Base-register addressing

ebx = 00000010h ax = 6789h ebx = 00404014h cx = 6789h

esi = 00404004h

.data

count dword 10h

array1 byte 10h,11h,12h,13h

array2 word 123h,234h,345h,456h

array3 dword 123456h, 23456789h

.code

main PROC

mov esi, offset arrayl mov ebx, 10h

mov ax, word ptr[ebx+esi]-

add ebx,esi

mov cx, word ptr[ebx]

call dumpregs

exit

main ENDP

(DumpRegs) mair

EAX=753E6789 EBX=00404014 ECX=00006789 EDX=00401005

ESI=00404004 EDI=00000000 EBP=0012FF94 ESP=0012FF8C

00404014: 89 00404015: 67 00404016: 45 00404017: 23

*Value:* array3

Offset:

Load a word size

value into ax

# Directives BYTE PTR, WORD PTR, DWORD PTR

To get around this instance, we must use a pointer directive, such as;

```

mov BYTE PTR [ESI], 5 ; Store 8-bit value

mov WORD PTR [ESI], 5 ; Store 16-bit value

mov DWORD PTR [ESI], 5 ; Store 32-bit value

```

- In general, PTR operator forces expression to be treated as a pointer of specified type

- E.g .data

num DWORD 0

.code

mov ax, WORD PTR (num) ;load a word-size value from a DWORD

## (f.3) Indexed Addressing

$$EA = A + R$$

- A = base

- R = displacement

- Good for accessing arrays

### .data array1 byte 10h,11h,12h,13h array2 word 123h,234h,345h,456h array3 dword 123456h,23456789h

### Exercise 4.1:

Given three arrays with multiple initializer in assembly language program. Complete the following diagram by writing:

- (a) the offset for all memory. Assume the first offset is 00404004.

- (b) the value of the data stored using Little Endian Order.

| Offset:   | Value: | Offset: | Value: |

|-----------|--------|---------|--------|

| 00404004: |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

|           |        |         |        |

### Displacement Addressing.

(3) Indexed addressing

mov bx, [array2+eax]

Add eax, 2

```

.data

array1 byte 10h,11h,12h,13h

array2 word 123h, 234h, 345h, 456h

array3 dword 123456h, 23456789h

.code

main PROC

mov eax, 0

Base

mov ecx, 4

L1:

mov bx, array2[eax]

add eax, 2

call dumpregs

LOOP L1

Displacement

exit

main ENDP

```

CX is known as the count register, as the ECX, CX registers store the loop count in iterative operations

### Displacement Addressing.

### (3) Indexed addressing

```

eax = 00000000h

```

$$ecx = 00000004h$$

```

bx = 0123h

```

eax = 00000002h

ecx = 00000003h

.data

array1 byte 10h,11h,12h,13h

array2 word 123h,234h,345h,456h

array3 dword 123456h, 23456789h

.code

main PROC

mov eax, 0

mov ecx, 4

#### L1:

mov bx, array2[eax] add eax,2

call dumpregs

LOOP L1

exit

main ENDP

mov bx, [array2+eax]

[00404008+00000000]

$\rightarrow$  array2[00404008]

dec ecx

dec ecx

### Displacement Addressing.

(3) Indexed addressing

```

bx = 0234h

eax = 00000004h

ecx = 00000002h

```

```

mov bx, array2[eax]

add eax,2

call dumpregs

LOOP L1

exit

main ENDP

[004040408+00000002]

```

→ array2[0040400A]

62

2<sup>nd</sup> looping

dec ecx

### Displacement Addressing.

(3) Indexed addressing

L1:

```

bx = 0345h

eax = 00000006h

ecx = 00000001h

```

```

mov bx, array2[eax]

add eax,2

call dumpregs

LOOP L1

exit

main ENDP

[00404008+00000004]

array2[0040400C]

```

63

3<sup>rd</sup> looping

### Displacement Addressing.

(3) Indexed addressing

bx = 0456h

eax = 00000008h

ecx = 00000000h

4<sup>th</sup> looping

**Exit looping**

L1:

mov bx, array2[eax]

add eax, 2

call dumpregs

LOOP **L1**

exit

main ENDP

mov bx, [array2+eax]

[00404008+00000006]

→ array2[0040400E]

dec ecx

### The DumpRegs for the program:

```

EAX=00000002 EBX=00000123 ECX=00000004 EDX=00000000 ESI=00404004 EDI=00404008 EBP=0012FF94 ESP=0012FF8C EIP=00401047 EFL=000000202 CF=0 SF=0 ZF=0 OF=0

```

```

EAX=00000004 EBX=00000234 ECX=00000003 EDX=00000000

ESI=00404004 EDI=00404008 EBP=0012FF94 ESP=0012FF8C

EIP=00401047 EFL=00000202 CF=0 SF=0 ZF=0 OF=0

```

```

EAX=0000006 EBX=00000345 ECX=00000002 EDX=00000000

ESI=00404004 EDI=00404008 EBP=0012FF94 ESP=0012FF8C

EIP=00401047 EFL=00000202 CF=0 SF=0 ZF=0 OF=0

```

```

EAX=00000008 EBX=00000456 ECX=00000001 EDX=00000000

ESI=00404004 EDI=00404008 EBP=0012FF94 ESP=0012FF8C

EIP=00401047 EFL=00000202 CF=0 SF=0 ZF=0 OF=0

```

### Table: Basic addressing modes.

| Mode              | Algorithm         | Principal Advantage | Principal Disadvantage     |

|-------------------|-------------------|---------------------|----------------------------|

| Immediate         | Operand = A       | No memory reference | Limited operand magnitude  |

| Direct            | EA = A            | Simple              | Limited address space      |

| Indirect          | EA = (A)          | Large address space | Multiple memory references |

| Register          | EA = R            | No memory reference | Limited address space      |

| Register indirect | EA = (R)          | Large address space | Extra memory reference     |

| Displacement      | EA = A + (R)      | Flexibility         | Complexity                 |

| Stack             | EA = top of stack | No memory reference | Limited applicability      |

# Module 4 Instruction Set Architecture (ISA)

- 4.1 Introduction

- 4.2 Machine Instruction Characteristics

- 4.3 Types of Operands

- 4.4 Addressing Modes

- 4.5 Instruction Formats

- 4.6 Summary

- Overview

- Instruction Length

- □ Allocation Bits

- Variable-Length Instructions

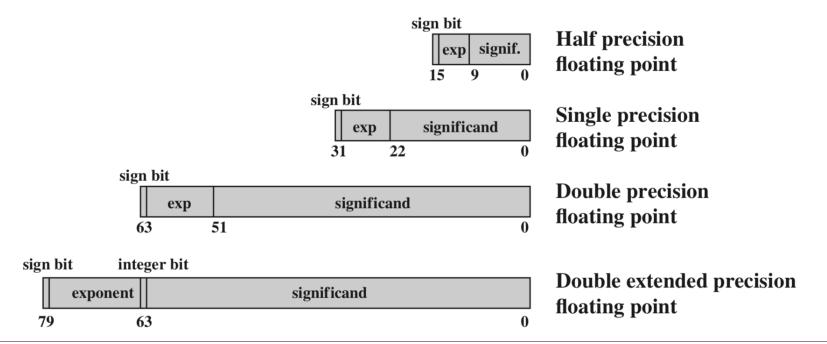

- An instruction format defines the layout of the bits of an instruction, in terms of its constituent fields.

- An instruction format must include an opcode and, implicitly or explicitly, zero or more operands.

- The format must, implicitly or explicitly, indicate the addressing mode for each operand.

- For most instruction sets, more than one instruction format is used.

### ■ Four common instruction formats:

(a) Zero-address instruction.

OPCODE

(b) One-address instruction

OPCODE ADDRESS

(c) Two-address instruction.

OPCODE | ADDRESS1 | ADDRESS2

(d) Three-address instruction.

OPCODE ADDR1 ADDR2 ADDR3

- This decision affects, and is affected by:

- memory size,

- memory organization,

- bus structure,

- processor complexity, and

- processor speed.

- Trade off between <u>powerful instruction</u> repertoire and <u>saving</u> <u>space</u>.

- Other issues: Instruction length equal or multiple to memory transfer length (bus system)?

We've looked at some of the factors that go into deciding the length of the instruction format.

An equally difficult issue is how to allocate the bits in that format, and the trade-offs here are complex.

- The following interrelated factors go into determining the use of the addressing bits:

- Number of addressing modes if indicated implicitly, certain opcodes might always call for indexing; if explicit – one or more mode bits will be needed.

- Number of operands typical instruction has 2 operands uses mode indicator for operand addresses.

- Register versus memory single user register (accumulator), one operand address is implicit and consume no instruction bits; for multiple registers – a few bits are needed to specify the registers.

- Number of register sets have one set of general purpose registers with 32 or more registers in the set for example for sets of <u>8 registers only 3 bits</u> are needed to identify the registers, <u>opcode will implicitly determine</u> which register set is being referenced.

- Address range the range of addresses that can be referenced related to the number of bits.

- □ Address granularity an address can reference a word or byte a the designer's choice – byte addressing is convenient for character manipulation.

# Variable-Length Instructions

- Designer may choose instead to provide a variety of instruction formats of different lengths.

- This tactic makes it easy to <u>provide a large repertoire</u> of opcodes, with different opcode lengths.

- Addressing can be more <u>flexible</u>, with various combinations of register and memory references plus addressing modes.

- With variable-length instructions, these many variations can be provided efficiently and compactly

# 4.6 Summary

- This chapter discussed on *what* an instruction set does by examining the types of operands and operations that may be specified by machine instructions.

- Described the various types of addressing modes common in instruction sets.

- Present an overview of essential characteristics of machine instructions.

- Summarize the issues and trade-offs involved in designing an instruction format.

### **Review Questions**

- 4.1 What are the typical elements of a machine instruction?

- 4.2 What types of locations can hold source and destination operands?

- 4.3 List and briefly explain five important instruction set design issues.

- 4.4 What types of operands are typical in machine instruction sets?

### **Review Questions**

### 4.5 Briefly define:

- a) immediate addressing.

- b) direct addressing.

- c) indirect addressing.

- d) register addressing.

- e) register indirect addressing.

- f) displacement addressing.

- g) relative addressing.

- 4.6 What are the advantages of using a variable-length instruction format?